The Preserve: Lehigh Library Digital Collections

## Algebraic Techniques For Finding Tests For Logical Faults In Digital Circuits.

## Citation

FLOMENHOFT, MARK JOEL. Algebraic Techniques For Finding Tests For Logical Faults In Digital Circuits. 1973, https://preserve.lehigh.edu/lehigh-scholarship/graduate-publications-theses-dissertations/theses-dissertations/algebraic-0.

Find more at https://preserve.lehigh.edu/

#### **INFORMATION TO USERS**

This material was produced from a microfilm copy of the original document. While the most advanced technological means to photograph and reproduce this document have been used, the quality is heavily dependent upon the quality of the original submitted.

The following explanation of techniques is provided to help you understand markings or patterns which may appear on this reproduction.

- 1. The sign or "target" for pages apparently lacking from the document photographed is "Missing Page(s)". If it was possible to obtain the missing page(s) or section, they are spliced into the film along with adjacent pages. This may have necessitated cutting thru an image and duplicating adjacent pages to insure you complete continuity.

- 2. When an image on the film is obliterated with a large round black mark, it is an indication that the photographer suspected that the copy may have moved during exposure and thus cause a blurred image. You will find a good image of the page in the adjacent frame.

- 3. When a map, drawing or chart, etc., was part of the material being photographed the photographer followed a definite method in "sectioning" the material. It is customary to begin photoing at the upper left hand corner of a large sheet and to continue photoing from left to right in equal sections with a small overlap. If necessary, sectioning is continued again beginning below the first row and continuing on until complete.

- 4. The majority of users indicate that the textual content is of greatest value, however, a somewhat higher quality reproduction could be made from "photographs" if essential to the understanding of the dissertation. Silver prints of "photographs" may be ordered at additional charge by writing the Order Department, giving the catalog number, title, author and specific pages you wish reproduced.

- 5. PLEASE NOTE: Some pages may have indistinct print. Filmed as received.

**Xerox University Microfilms**

300 North Zeeb Road Ann Arbor, Michigan 48106

74-11,346

FLOMENHOFT, Mark Joe1, 1945-ALGEBRAIC TECHNIQUES FOR FINDING TESTS FOR LOGICAL FAULTS IN DIGITAL CIRCUITS.

Lehigh University, Ph.D., 1973 Engineering, electrical

University Microfilms, A XEROX Company, Ann Arbor, Michigan

# ALGEBRAIC TECHNIQUES FOR FINDING TESTS FOR LOGICAL FAULTS IN DIGITAL CIRCUITS

bу

Mark Joel Flomenhoft

A Dissertation

Presented to the Graduate Committee

of Lehigh University

in Candidacy for the Degree of

Doctor of Philosophy

Electrical Engineering

in

Lehigh University

1973

Approved and recommended for acceptance as a dissertation in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Dec. 10, 1973

Offied K. Susskind Professor in Charge

Accepted\_\_\_\_\_

Special committee directing the doctoral work of Mr. Mark J. Flomenhoft

Alfred K. Susskind

Chairman

Thomas F Arnold

William A. Barrett

#### **ACKNOWLEDGMENT**

I wish to express deep appreciation to Professor Alfred K. Susskind for his role as dissertation supervisor. His encouragement and the many discussions we held were an invaluable assist to me in completing my research.

I would also like to thank the other members of my thesis committee -- Dr. Thomas F. Arnold, Dr. William A. Barrett, and Dr. Kenneth K. Tzeng -- for their helpful comments and suggestions.

Financial support by Bell Telephone Laboratories is gratefully acknowledged.

## TABLE OF CONTENTS

|          |                                                                           |                                                                     | Page |

|----------|---------------------------------------------------------------------------|---------------------------------------------------------------------|------|

| Abs      | tract                                                                     | ;<br>;                                                              | 1    |

| 1.       | Introduction                                                              |                                                                     |      |

|          | 1.1                                                                       | Fundamental Assumptions and Additional Constraints                  | 3    |

|          | 1.2                                                                       | Properties of Algebraic Techniques for Finding Tests                | 6    |

|          | 1.3                                                                       | Labeling the Circuit Leads                                          | 7    |

|          | 1.4                                                                       | Simply-Indistinguishable Single Stuck-at Faults                     | 9    |

|          | 1.5                                                                       | Outline of the Following Chapters and Summary of Results            | 14   |

| 2.       | The                                                                       | SP00F                                                               | 17   |

|          | 2.1                                                                       | Construction of Network SPOOF's                                     | 17   |

|          | 2.2                                                                       | Properties of SPOOF's                                               | 23   |

| 3.       | Using SPOOF's to Find Tests for Several Fault Types                       |                                                                     |      |

|          | 3.1                                                                       | The Boolean-Difference Method for Finding Tests for Stuck-at Faults | 30   |

|          | 3.2                                                                       | The Direct-Difference Method for Finding Tests for Stuck-at Faults  | 32   |

|          | 3.3                                                                       | Comparison of the Boolean-Difference and Direct-Difference Methods  | 34   |

| <b>-</b> | 3.4                                                                       | Finding Tests for Regional Faults                                   | 36   |

|          | 3.5                                                                       | Finding Tests for Short Circuits                                    | 38   |

|          | 3.6                                                                       | Finding Tests for Shorted Gate-Input Diodes                         | 40   |

|          | 3.7                                                                       | Multi-Output Networks                                               | 43   |

| 4.       | Dynamically-Detectable Faults                                             |                                                                     | 45   |

|          | 4.1                                                                       | T-Expressions: Network Functions that Express Signal Delays         | 46   |

|          | 4.2                                                                       | Finding Tests for Dynamically-Detectable Faults                     | 48   |

| 5.       | Algebraic Analysis of Level-Input Fundamental-Mode<br>Sequential Circuits |                                                                     | 54   |

|          | 5.1                                                                       | Level-Input Fundamental-Mode Sequential Circuits                    | 55   |

|          | 5.2                                                                       | Stable-States (Steady-State) Analysis                               | 58   |

|          | <b>5</b> 7                                                                | Transition-Time (Transient) Analysis                                | 60   |

| <ul> <li>5.4 Synchronous-Equivalent Circuits</li> <li>5.5 Sequence-Response Expressions for LIFMSC's; Finding Synchronizing Sequences</li> <li>5.6 Reducing the Number of Variables</li> <li>6. Finding Tests for Level-Input Fundamental-Mode Sequential Circuits</li> <li>6.1 The Direct Difference for LIFMSC's</li> <li>6.2 Computational Considerations</li> <li>6.3 An Upper Bound on the Length of Test Sequences</li> <li>6.4 Identifying Undetectable Faults</li> <li>6.5 Tests for Complete Sets of Faults</li> </ul> | 67 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Finding Synchronizing Sequences  5.6 Reducing the Number of Variables  6. Finding Tests for Level-Input Fundamental-Mode Sequential Circuits  6.1 The Direct Difference for LIFMSC's  6.2 Computational Considerations  6.3 An Upper Bound on the Length of Test Sequences  6.4 Identifying Undetectable Faults  6.5 Tests for Complete Sets of Faults                                                                                                                                                                          | 0, |

| <ul> <li>6. Finding Tests for Level-Input Fundamental-Mode Sequential Circuits</li> <li>6.1 The Direct Difference for LIFMSC's</li> <li>6.2 Computational Considerations</li> <li>6.3 An Upper Bound on the Length of Test Sequences</li> <li>6.4 Identifying Undetectable Faults</li> <li>6.5 Tests for Complete Sets of Faults</li> </ul>                                                                                                                                                                                     | 68 |

| Circuits 6.1 The Direct Difference for LIFMSC's 6.2 Computational Considerations 6.3 An Upper Bound on the Length of Test Sequences 6.4 Identifying Undetectable Faults 6.5 Tests for Complete Sets of Faults                                                                                                                                                                                                                                                                                                                   | 78 |

| <ul> <li>6.2 Computational Considerations</li> <li>6.3 An Upper Bound on the Length of Test Sequences</li> <li>6.4 Identifying Undetectable Faults</li> <li>6.5 Tests for Complete Sets of Faults</li> </ul>                                                                                                                                                                                                                                                                                                                    | 81 |

| <ul><li>6.3 An Upper Bound on the Length of Test Sequences</li><li>6.4 Identifying Undetectable Faults</li><li>6.5 Tests for Complete Sets of Faults</li></ul>                                                                                                                                                                                                                                                                                                                                                                  | 81 |

| <ul><li>6.4 Identifying Undetectable Faults</li><li>6.5 Tests for Complete Sets of Faults</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                             | 85 |

| 6.5 Tests for Complete Sets of Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90 |

| 6.6. Summers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91 |

| 6.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92 |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94 |

| Vita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97 |

## LIST OF THEOREMS

|     |                                                                                                                           | Page |

|-----|---------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | There are a pair of SI sets associated with every single-input gate.                                                      | 10   |

| 1.2 | There is an SI set associated with every multi-<br>input gate.                                                            | 10   |

| 1.3 | For a fanout-free circuit the number of SI sets is $N_{M}^{+2}$ .                                                         | 11   |

| 1.4 | The number of fanout-free subcircuits of a given circuit is $N_Q$ .                                                       | 12   |

| 1.5 | For an arbitrary circuit the number of SI sets is $^{N}\mathbf{M}^{+2N}\mathbf{Q}$ .                                      | 12   |

| 2.1 | In constructing SPOOF's, no algebraic simplifications are possible.                                                       | 20   |

| Ź.2 | The expression obtained when the path lists are removed is the network function.                                          | 21   |

| 2.3 | The expression obtained when the path lists are removed is the network E-expression.                                      | 22   |

| 2.4 | Given the output SPOOF of a gate, the function and input SPOOF's of the gate can be determined.                           | 23   |

| 2.5 | Given a network SPOOF, the gate-level topology of the network and each of the internal lead SPOOF's can be reconstructed. | 24   |

| 2.6 | Decompositions can be determined by Procedure 2.5.                                                                        | 25   |

| 2.7 | The output function when some pattern of stuck-at faults is present can be determined by Procedure 2.4.                   | 26   |

| 2.8 | Internal lead functions can be determined by Procedure 2.5.                                                               | 28   |

| 5.1 | The response of a gate to an input change can be determined by Procedure 5.1.                                             | 60   |

| 5.2 | The transition time and sets P and I can be determined by Procedure 5.2.                                                  | 64   |

| 6.1 | An upper bound on the length of a test sequence                                                                           |      |

|     | for a fault in a finite-state machine is $\frac{p(p+1)}{2}$ .                                                             | 87   |

| 6.2 | An upper bound on the length of a test sequence for a fault in an LIFMSC is $\frac{p(p+1)}{2}$ .                          | 90   |

## LIST OF PROCEDURES

|     |                                                                                 | Page |

|-----|---------------------------------------------------------------------------------|------|

| 1.0 | Labeling the circuit leads                                                      | 7    |

| 2.1 | Constructing SPOOF's                                                            | 18   |

| 2.2 | Determining gate levels                                                         | 20   |

| 2.3 | Determining decompositions                                                      | 25   |

| 2.4 | Determining the output function when some pattern of stuck-at faults is present | 27   |

| 2.5 | Determining internal lead functions                                             | 28   |

| 3.1 | Finding tests for regional faults                                               | 36   |

| 3.2 | Finding tests for short circuits                                                | 39   |

| 3.3 | Finding tests for shorted gate-input diodes                                     | 42   |

| 4.0 | Finding dynamic tests                                                           | 48   |

| 5.1 | Finding the response of a gate to an input change                               | 60   |

| 5.2 | Finding the transition time and sets P and I                                    | 64   |

| 5.3 | Finding sequence-response expressions                                           | 70   |

## LIST OF FIGURES

|     |                                                                      | Page |

|-----|----------------------------------------------------------------------|------|

| 1.1 | Various lead-labeling schemes                                        | 8    |

| 1.2 | Circuit for examples                                                 | 14   |

| 3.1 | Circuit to illustrate the effect of a shorted gate-input diode fault | 41   |

| 3.2 | Typical DTL gate                                                     | 41   |

| 4.1 | Networks N1 and N2                                                   | 45   |

| 4.2 | Network N1 with gate-input delay-variables                           | 51   |

| 4.3 | A one-shot and a pulse multiplier                                    | 52   |

| 5.1 | NAND latch                                                           | 56   |

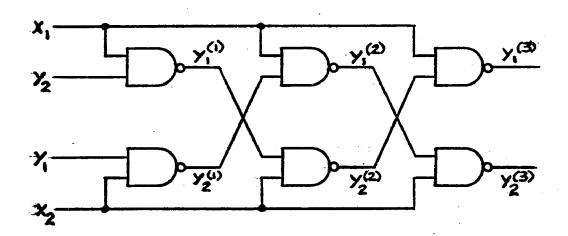

| 5.2 | Cascade of three cells for the NAND latch                            | 61   |

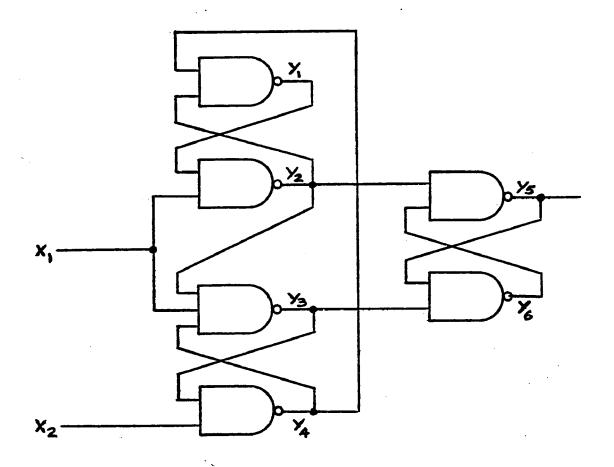

| 5.3 | Positive-edge-triggered type-D flip-flop                             | 74   |

| 5.4 | Negative-edge-clocked master-slave JK flip-flop                      | 76   |

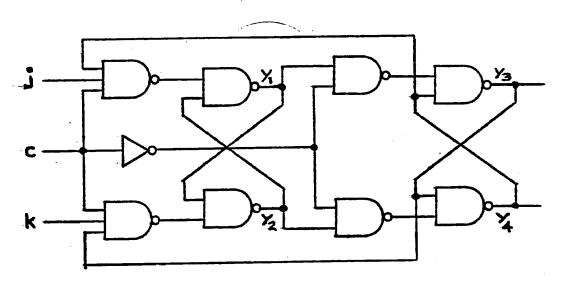

| 6.0 | Positive-edge-triggered type-D flip-flop                             | 83   |

#### **ABSTRACT**

Algebraic techniques are used to find tests for permanent logical faults in combinational and sequential digital circuits. Circuits are assumed to be specified solely as an interconnection of gates; flip-flops, feedback loops, state variables, etc., need not be identified. Also, no assumptions are made about reconvergent fanout, redundancy, or the initial state of a sequential circuit.

Fundamental to the procedures for combinational circuits is the SPOOF, an algebraic notation that expresses the topology of a network as well as its logical function. Both fault-free and faulty behavior are readily characterized by the SPOOF, and it is shown how to obtain (1) all the test vectors for any given regional fault, which alters the function of some subnetwork in an arbitrary but specified manner; (2) all the test vectors for any given "logical" short circuit, i.e., an unintended connection between signal leads that behaves like a wired logic AND or OR; (3) all the test vectors for any given shorted gate-input diode, a fault characteristic of certain logic families; and (4) all the test vectors for any given combination of stuckat faults. Also considered are faults that either cause unintended output pulses or inhibit intended output pulses. Such faults, which have traditionally been called "undetectable", are detectable by "dynamic tests". It is shown how to modify the SPOOF so that dynamic tests can be found.

Sequential circuits are analyzed by a new algebraic method

that employs the unit-gate-delay timing model. First a "static"

the primary inputs and the gates. Then a "transient" analysis determines the maximum number of gate delays before a circuit attains a stable state after the input vector is changed. At the same time, those input changes that cause circuit oscillation under the unit-gatedelay timing model are identified. Using these results, the response of a circuit to sequences of any given length can be characterized, and both synchronizing sequences and test sequences are found. The tests obtained are independent of initial state and, like the synchronizing sequences obtained, are guaranteed not to cause circuit oscillation under the unit-gate-delay model. Included in the test generation method is a procedure for identifying at least some undetectable faults from the expressions for the response to a single input vector.

#### CHAPTER 1

## INTRODUCTION

A fault-detection test for a digital circuit is a sequence of input combinations that enables one to determine whether or not a given unit on hand satisfies its intended logical specification. In the case of combinational logic, an "exhaustive" test -- one consisting of all possible input vectors -- will detect any fault that does not make the circuit non-combinational (i.e., either sequential or non-digital). However, for a circuit with m binary inputs the length of such a test is 2<sup>m</sup>, which is unacceptably large in many instances.

The alternative to exhaustive testing is to find tests specifically to check for the presence of particular faults. For example, due to a fault a circuit lead may be permanently fixed ("stuck") in a logical state or a pair of leads may be unintentionally connected ("shorted"). By limiting the converage of a test to specified classes of faults, tests can usually be obtained that are orders of magnitude shorter than an exhaustive test. Although a non-exhaustive test is unlikely to detect every possible fault, experience suggests that the probability of a fault occurring that is undetected by such a test is small, provided only that the test does detect some "reasonable" class of faults -- every single stuck-type fault, for example.

## 1.1 Fundamental Assumptions and Additional Constraints

This dissertation presents algorithms for finding tests for

faults in combinational and sequential digital circuits. In developing

these algorithms, we have adhered to six fundamental assumptions:

- We consider only <u>binary</u> digital circuits, which means that the logical signals are two-valued.

- 2. We consider only gate-type digital circuits, where by a "gate" we mean a circuit block that implements one of the functions AND, OR, NOT, NAND, and NOR, or one of these functions with some number of complementing inputs.

- The only combinational circuits we consider are those that are loop-free.

- 4. The only sequential circuits we consider are those that are <a href="Level-input">Level-input</a> (the circuit senses input levels rather than input pulses) and <a href="fundamental-mode">fundamental-mode</a> (given that the inputs are held constant for a sufficient time, the circuit will reach a stable state).

- 5. We consider only permanent logical faults, which means that the effect of a fault is to transform one gatetype binary digital circuit (the "intended" or "faultfree" circuit) into another (a "faulty" circuit).

- 6. Our goal is a unified theory applicable to a variety of fault types.

Assumptions 1 through 4 make explicit that we are considering the type of logic circuitry used in contemporary digital systems. Assumptions one and two exclude types of circuitry now only of theoretical interest, such as multi-level logic and threshold logic.

Also, we do not investigate extensions of our algorithms for circuits with "wired" logic (gate outputs tied together to realize wired-AND's and wired-OR's) or unconventional gate types (such as bilateral transmission gates and "tri-state" gates) or for contact-type (relay) circuits. (Bilateral transmission gates, a feature of MOS technology, are sometimes used as bidirectional gates and as dynamic-memory flip-flops. Tri-state gates have three output states -- logic 0, logic 1, and "high impedance.")

The assumption of circuits that are loop-free combinational or fundamental-mode sequential is compatible with most actual circuits. Looped combinational logic has only recently been recognized as a possibility [1], and its occurrences are rare. The restriction to level-input fundamental-mode sequential circuits includes most all sequential circuits, the two types of which are synchronous ("clocked") and asynchronous ("unclocked"). However, circuits of each type can be found that are pulse-input or non-fundamental-mode, and for these the applicability of our algorithms has not been investigated.

The fifth assumption -- that faults are permanent (or "solid") -- assures that results obtained throughout a test sequence are consistent. We do not consider intermittent faults, which greatly complicate the testing problem. (For a discussion on intermittent faults, see [2].)

As a consequence of the goal of obtaining a unified theory applicable to a variety of fault types, we avoid approaches tailored

to characteristics of special fault types. But then we know of no alternative to finding tests for one fault at a time.

Besides the assumptions above we impose four additional constraints that are, we believe, typical for a manufacturing environment:

- A circuit is specified solely as an interconnection of gates. Supplementary descriptive information -- a state table, the designation of "state variables", etc. -- is assumed unavailable.

- Changing the circuit to enhance testability -- adding auxiliary inputs or outputs or opening feedback loops -is disallowed.

- 3. The given circuit may be "redundant" in the sense that there may exist no tests for some faults.

- 4. We desire "completeness" in the sense that if a test to detect a fault does exist, our procedures should produce it.

## 1.2 Properties of Algebraic Techniques for Finding Tests

All of our techniques for finding tests are based on Boolean algebra. Specifically, tests for a fault are the solutions to a Boolean equation of the form E=1, where E is a Boolean expression.

Test generation procedures formulated in this way have several advantageous properties:

Trial-and-error techniques are avoided. For a given fault we simply determine the appropriate Boolean expression E and solve the equation E=1.

- 2. An undetectable fault is signified when E=1 has no solutions, i.e., when E is identically zero.

- A unified theory applicable to a variety of fault types can be obtained.

- 4. All tests for a given fault are found simultaneously.

These are the multiple solutions to the equation E=1.

- 5. The tests are "minimally-constrained" in the sense that only the inputs that must be set to particular values are specified.

## 1.3 Labeling the Circuit Leads

Logical faults are characterized by the way they affect logic signals at various locations in a circuit. It has been found convenient to denote locations in a circuit in terms of leads rather than gates. The scheme we use for labeling the leads, appropriate for sequential as well as combinational circuits, is as follows:

## Procedure 1.0

- Assign a distinct integer label to each primary input lead and gate output lead. After this is done the only unlabeled leads are fanout branches.

- 2. To each of the k fanout branches from a lead labeled p assign a distinct label of the form pa, where a is one of the first k letters in some alphabet. Repeat this step until all the leads are labeled.

We have two reasons for the special labeling of fanout

branches. First, tests are commonly designed to specifically check for

the presence of a single fault. However, when tests are generated using a circuit model that does not faithfully represent the actual wiring topology, some real single faults may remain untested. For example, an open circuit along lead 9b in Fig. 1.1(c) is a failure that can be modeled as a single stuck-type fault. However, this failure is not represented by any single fault in the circuit models of Fig. 1.1(a) and 1.1(b). Thus a single-fault test based on either of these models does not necessarily test all real single faults. The lead-labeling scheme used here allows us, if we choose, to model circuit wiring accurately.

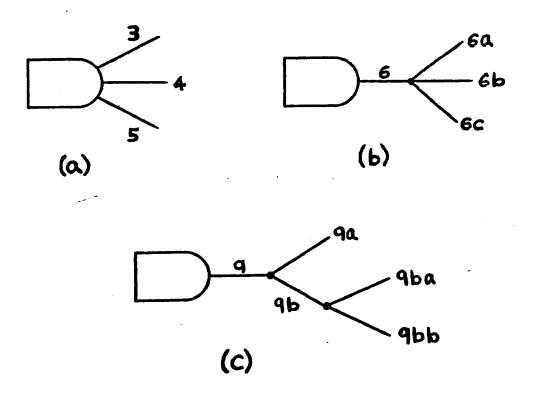

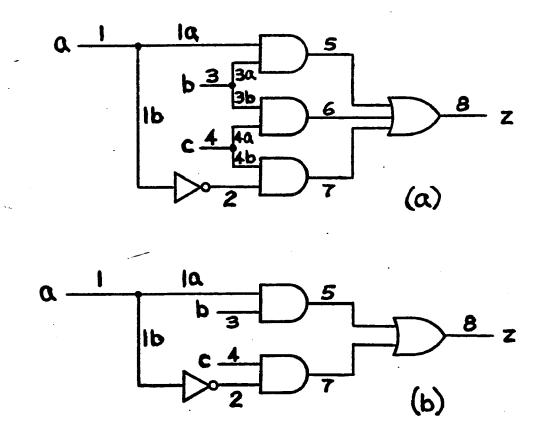

Figure 1.1. (a) Labeling that ignores fanout. (b) Labeling that defines fanout but ignores actual wiring topology. (c) Labeling that defines fanout and actual wiring topology.

Our second reason for explicitly labeling fanout branches is that finding tests for certain types of faults -- short circuits, for example -- requires the identification of fanout branches. Labeling the leads as we do thus simplifies test generation, which is described in Chapter 3.

## 1.4 Simply-Indistinguishable Single Stuck-at Faults

A <u>single stuck-at fault</u> is any malfunction that causes a single lead in a circuit to be permanently fixed in the 0-state ("stuck-at-0") or permanently fixed in the 1-state ("stuck-at-1"). It is popular to use the set of all single stuck-at faults as the class of faults for which tests are specifically found. We now show that, although a circuit with N leads has 2N possible single stuck-at faults, by inspecting the gate-level circuit diagram one can always reduce the number of faults for which tests need individually be found to about 1.2N.

As has been observed by Hayes [3] and Schertz and Metze [4], a set of indistinguishable single stuck-at faults is associated with every gate in a digital circuit. For example, if <u>i</u> is an input and <u>p</u> is the output of an AND-gate, then there is no test that can distinguish between i@0 and p@0. (We use the notation k@v to mean "lead k stuck-at-v".) Such faults will be called <u>simply-indistinguishable</u>, SI, and a test need be found for only one fault in each set of SI faults.

Consider a digital circuit with N leads. We partition the set of leads into three classes, as follows: S, the set of all leads

that are inputs to single-input gates; M, the set of all leads that are inputs to multi-input gates; and Q, the set of all other leads -- the primary output leads and all leads that fan out. Let  $N_S$ ,  $N_M$ , and  $N_Q$  denote the sizes of these sets. We show that, by inspecting the gate-level circuit diagram, the 2N possible single stuck-at faults can be merged into  $N_M + 2N_Q$  SI sets.

## Theorem 1.1

If G is a single-input gate, then associated with G are a pair of SI sets each consisting of a single stuck-at fault on the input lead and the output lead, and these sets can be specified.

## Proof

Let G have input lead i and output lead p. If G is non-inverting [inverting], then i@O is indistinguishable from p@O [p@1] and i@1 is indistinguishable from p@I [p@O]. Thus {i@O, p@O} and {i@1, p@1} [{i@O, p@1} and {i@1, p@O}] are SI sets.

#### Theorem 1.2

If G is a multi-input gate, then associated with G is an SI set consisting of a single stuck-at fault on each input lead and the output lead, and this set can be specified.

## Proof

Let G have n inputs i,j,...,m and output lead p. For the class of gates defined (AND, OR, NAND, or NOR, possibly with some inverting inputs), the logic-state of p is v for some particular input vector  $(u_i, u_i, \dots, u_m)$  and  $\bar{\mathbf{v}}$  for all the other  $2^n$ -1 input vectors.

Then  $k@\bar{u}_k$  is indistinguishable from  $p@\bar{v}$  for every input k, and  $\{i@\bar{u}_i, j@\bar{u}_i, \cdots, m@\bar{u}_m, p@\bar{v}\}$  is an SI set.

## Definition

A digital circuit is <u>fanout-free</u> if it has a single primary output and every lead other than the primary output is a gate input.

#### Theorem 1.3

By inspecting the gate-level diagram of a fanout-free digital circuit, the 2N possible single stuck-at faults can be merged into  $N_M+2$  SI sets, and these sets can be specified.

## Proof

We account for the primary output faults by starting with two fault sets, each consisting of one of these faults. We account for all the other faults as follows:

Suppose G is a single input gate whose output faults have been accounted for. By Theorem 1.1, each input fault of G can be merged into an existing fault set. Thus we account for both of the input faults of G without adding any new fault sets.

Suppose G is a multi-input gate whose output faults have been accounted for. By Theorem 1.2, half the input faults of G can be merged into an existing fault set. Thus we account for all the input faults of G by adding one new fault set for each input.

Thus to account for all 2N faults, precisely  $N_M^{+2}$  fault sets are required. That these sets can be specified is evident, because the proof is constructive (it consists of a procedure).

## Definition

A circuit C' is a <u>subcircuit</u> of a digital circuit C if C' can be obtained by deleting some number of leads and/or gates from C. Then C is said to <u>contain</u> C'; and if C' is not identical to C, i.e., if the number of deletions is not zero, then the containment is <u>proper</u>. Also, a fanout-free subcircuit C' of a digital circuit C is <u>maximal</u> if no other fanout-free subcircuit of C properly contains C'.

## Theorem 1.4

The number of maximal fanout-free subcircuits of a digital circuit is precisely  $N_Q$ , the total number of primary output leads and leads that fan out.

## Proof

Every primary output lead and every lead that fans out is the output of a maximal fanout-free subcircuit, and no other lead -- a gate input -- is the output of a maximal fanout-free subcircuit. Thus the number of maximal fanout-free subcircuits of a digital circuit is precisely  $N_Q$ .

## Theorem 1.5

By inspecting the gate-level diagram of a digital circuit, the 2N possible single stuck-at faults can be merged into  $N_M^+$   $^{2N}Q$   $^{SI}$  sets, and these sets can be specified.

## Proof

It is easily seen that the set of all maximal fanout-free subcircuits of a given digital circuit is a partition on that circuit.

Thus, by Theorems 1.3 and 1.4, the 2N possible single stuck-at faults can be merged into

$$\sum_{i=1}^{N_Q} (N_{Mi}^+ 2) = N_{M}^+ 2N_Q$$

SI sets. That these sets can be specified is evident, because the SI sets for each subcircuit can be specified.

## Example 1.0

Figure 1.2 is the gate configuration for a simple network. The total number of leads N is 12, and  $N_M=8$  and  $N_Q=3$ . Thus there are  $N_M+2N_Q=14$  SI sets for this circuit. They are as follows (the lead-labeling is according to Procedure 1.0):

{100,2a01,5a00,600} {2b01,301,401,501} {601,5b00,701,801} {5b01,700}

All the other faults -- 101, 200, 201, 2a00, 2b00, 300, 400, 500, 5a01, and 800 -- are in individual sets. The total number of sets is 14, as it must be for this circuit. Note that the "faults-to-leads" ratio is  $\frac{14}{12}$ , or about 1.2.

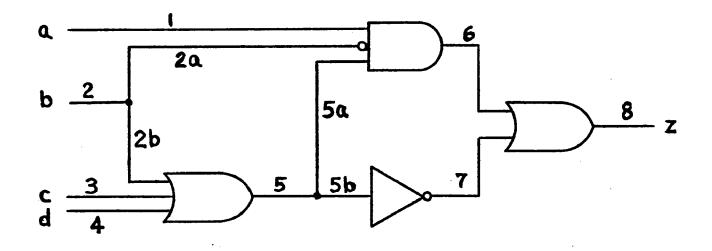

Figure 1.2. Circuit for examples.

Let us restate the result of Theorem 1.5 in the form of a "faults-to-leads" ratio R -- R =  $\frac{N_M^{+2N}Q}{N}$ . Using  $N_M^{+N}Q = N-N_S$ , we obtain R = 1+  $\frac{N_Q^{-N}S}{N}$ . Typically, R turns out to be about 1.2, which means that about 40% of the 2N single stuck-at faults can be eliminated. Note that this result applies to sequential as well as combinational circuits.

## 1.5 Outline of Following Chapters and Summary of Results

In Chapter 2 we define the SPOOF, an algebraic notation by which both fault-free and faulty behavior of loop-free logic networks can be characterized. It is proved that the SPOOF expresses the topology as well as the function of a network. Procedures are given for determining the logical function at any point within a circuit in terms of the primary input variables and for determining the output

function in terms of any given set of lead variables and the input variables.

The procedures of Chapter 2 are the basis of techniques for algebraically finding tests under a variety of fault models. In Chapter 3 we show how tests can be obtained for stuck-at faults by an existing method called the "Boolean difference" and a new method we call the "direct difference". The two approaches are compared, and the direct difference is shown to be more efficient than the Boolean difference. Procedures are also given to find tests for several kinds of faults not of the stuck-at type: regional faults, each of which alters the function of some subnetwork in an arbitrary but specified manner; logical short circuits, unintended connections between signal leads that behave like wired-logic AND's or OR's; and shorts in gate-input diodes, a failure mode exhibited by certain logic families.

In Chapter 4 we consider faults that either cause unintended output pulses or inhibit intended output pulses. Such faults, which have traditionally been called "undetectable", are detectable by "dynamic tests". We show how the direct difference can be used to find dynamic tests when the SPOOF is modified to account for propagation delays.

Chapter 5 introduces a new method for analyzing level-input fundamental-mode sequential circuits. First we do a "static" analysis that determines all possible steady-state combinations of values for the primary inputs and the gates. Then we do a "transient"

analysis that determines the maximum number of gate delays before a circuit attains a stable state after the input vector is changed. At the same time, those input changes that cause circuit oscillation under the unit-gate-delay timing model are identified. Using these results, we show how to characterize the response of a circuit to sequences of any given length. The problem of finding synchronizing sequences (initializing sequences independent of starting state) is an important application of the "sequence-response" expressions obtained, and examples are used to illustrate the power of the technique.

In Chapter 6 the algebraic techniques presented in Chapter 5 are used as the basis of a method for finding tests for individual faults. The tests obtained are independent of initial state and guaranteed not to cause circuit oscillation under the unit-gate-delay timing model. The algorithm is based solely on the gate-level circuit description, and no heuristic "loop-cutting" is involved.

#### CHAPTER 2

#### THE SPOOF

The structure and parity-observing output function, SPOOF, was originated by F. W. Clegg as an algebraic notation to characterize the topology as well as the function of a loop-free logic network [5]. (A similar notation was developed independently by S. C. Si [6].) This characterization is achieved by associating with the algebraic input literals path lists that contain interconnection and inversion-parity data. This chapter describes the construction of SPOOF's and details properties important for fault analysis. Although single-output networks are implicitly assumed, all the results are applicable to multi-output networks by treating the outputs individually.

## 2.1 Construction of Network SPOOF's

whereas the algebraic variables in a conventional Boolean expression for a logic network are <u>literals</u> -- primary inputs and their complements -- the variables in a SPOOF are literals together with <u>path lists</u>. Each path list is a sequence of lead labels i,j,...,p such that, for every subsequence m,n of adjacent labels, either m is an input to a gate whose output is n or m is a lead that fans out into n. For lack of a better name we call a literal together with a path list a term.

As will be shown (Theorem 2.5), when the path lists designate inversion parity as well as the lead interconnections, then a network can be reconstructed from its SPOOF alone. The representation of inversion parity is accomplished by using two types of path list

entries -- lead labels and their "complements" -- which for the lead label  $\underline{k}$  are denoted k and  $\bar{k}$ , respectively.

## Definition

The <u>complement of a path list entry</u> e [e] is e [e]. The <u>complement of a path list</u> is obtained by complementing each entry in the list. The <u>complement of a term</u> is obtained by complementing both the input literal and the path list.

Let S<sub>p</sub> be the SPOOF for lead p expressed in terms of primary input literals and in sum-of-products form. (Other standard forms -- product-of-sums, AND/exclusive-OR, etc. -- could be used as well.)

The procedure for obtaining SPOOF's for the leads in a circuit is as follows:

## Procedure 2.1

- 1. If **p** is the primary input lead for input variable  $x [\bar{x}]$ , then  $S_p$  is the term  $x_p [\bar{x}_p]$ .

- 2. Suppose G is a gate with input leads i,j,...,m and output lead p. If  $y_i, y_j, ..., y_m$  are the Boolean input-lead functions and G implements the function  $f_G(y_i, y_j, ..., y_m)$ , then  $S_p$  is  $f_G(S_i, S_j, ..., S_m)$  expressed in sum-of-products form and with p appended to every path list. In performing algebraic manipulations, SPOOF terms are treated like literals in conventional Boolean algebra. However, terms with path lists that are different (non-identical and non-complementary) are to be considered distinct algebraic variables.

3. If p is a fanout branch from lead m, then  $S_p$  is  $S_m$  with p appended to every path list.

## Example 2.1

Figure 1.2 is a gate configuration that realizes the function  $z = a\bar{b} + b\bar{c}\bar{d}$ . The network SPOOF, S<sub>8</sub>, is obtained as follows:

| $S_1 = a_1$                                                                                                                                     | [Rule 1 of            | F Procedure 2.1] |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|

| $S_2 = b_2$                                                                                                                                     |                       | [Rule 1]         |

| $S_{2a} = (S_2)_{2a} = b_{2,2a}$                                                                                                                |                       | [Rule 3]         |

| $S_{2b} = (S_2)_{2b} = b_{2,2b}$                                                                                                                |                       | [Rule 3]         |

| $S_3 = C_3$                                                                                                                                     |                       | [Rule 1]         |

| $S_4 = d_4$                                                                                                                                     |                       | [Rule 1]         |

| $S_5 = (S_{2b} + S_3 + S_4)_5 = b_{2,2b,5} + c_{3,5} + d_{4,5}$                                                                                 |                       | [Rule 2]         |

| $S_{5a} = (S_5)_{5a} = b_{2,2b,5,5a} + c_{3,5,5a} + d_{4,5}$                                                                                    | ,5a                   | [Rule 3]         |

| $S_{5b} = (S_5)_{5b} = b_{2,2b,5,5b} + c_{3,5,5b} + d_{4,5}$                                                                                    | ,5b                   | [Rule 3]         |

| $S_6 = (S_1 \cdot \overline{S}_{2a} \cdot S_{5a})_6 = a_{1,6} \overline{b}_{\overline{2},\overline{2a},6} b_{2,2b},$                            | 5,5a,6                | [n : a]          |

| $^{+a}_{1,6}$ , $^{\bar{b}}_{2,2a,6}$ , $^{c}_{3,5,5a,6}$ , $^{+a}_{1,6}$ , $^{\bar{b}}_{2,2a,6}$                                               | <sup>d</sup> 4,5,5a,6 | [Rule 2]         |

| $S_7 = (\bar{S}_{5b})_7 = \bar{b}_{\bar{2}, 2\bar{b}, \bar{5}, 5\bar{b}, 7} \bar{c}_{\bar{3}, \bar{5}, 5\bar{b}, 7} \bar{d}_{\bar{4}, \bar{5}}$ | , <del>5b</del> ,7    | [Rule 2]         |

| $S_8 = (S_6 + S_7)_8 = a_{1,6,8} \bar{b}_{2,2a,6,8} b_{2,2b,5,6}$                                                                               | 5a,6,8                |                  |

| $^{+a}$ 1,6,8 $^{\bar{b}}$ 2, $^{2a}$ ,6,8 $^{c}$ 3,5,5a,6,8                                                                                    |                       |                  |

| $^{+a}$ 1,6,8 $^{\bar{b}}$ 2, $^{2a}$ ,6,8 $^{d}$ 4,5,5a,6,8                                                                                    |                       | [Rule 2]         |

| +b2,2b,5,5b,7,8 <sup>c</sup> 3,5,5b,7,8 <sup>d</sup> 4,5,5b                                                                                     | 7,8                   |                  |

Rule 2 of Procedure 2.1 states that terms whose path lists are different are to be considered distinct algebraic variables. Thus if J and K are different path lists, all of the following are

irreducible:  $x_J x_K$ ,  $x_J + x_K$ ,  $x_J x_{\bar{K}}$ , and  $x_J + x_{\bar{K}}$ . The full consequence of this rule is that <u>no</u> algebraic simplifications are possible in forming SPOOF's. We prove this result using induction on the <u>level</u> of gates in a circuit. Gate levels are determined as follows:

## Procedure 2.2

- 1. Primary input leads and their fanouts are level zero.

- 2. Let G be a gate all of whose inputs are level k or less and with at least one level-k input. Then G, its output lead, and all its fanouts are level k+1.

## Theorem 2.1

In constructing SPOOF's according to Procedure 2.1, no algebraic simplifications are possible.

## Proof

Let G be a gate with input leads i,j,...,m and output lead p. Let  $\stackrel{\circ}{S}_p$  be  $\stackrel{\circ}{S}_p$  with p omitted from the path lists. For the class of gates defined either  $\stackrel{\circ}{S}_p = S_i^* S_j^* \cdots S_m^*$  or  $\stackrel{\circ}{S}_p = S_i^* + S_j^* + \cdots + S_m^*$ , where  $S_k^*$  is  $S_k$  or  $\bar{S}_k$ .

Suppose G is level <u>one</u>. Each SPOOF for the input leads of G is itself irreducible, for each consists of a single term. Each of the input leads of G is distinctly labeled (by Procedure 1.0), so in constructing  $\hat{S}_p$ , hence  $S_p$ , according to Procedure 2.1, no algebraic simplifications are possible.

Suppose G is level k, k>1. By inductive hypothesis, each SPOOF for the input leads of G is itself irreducible. Then because the input leads of G are distinctly labeled, in constructing  $S_{\rm p}$

according to Procedure 2.1, no algebraic simplifications are possible.

Theorem 2.1 is of computational significance, for it means that one can omit trying to reduce SPOOF expressions by the application of algebraic identities. Furthermore, as a corollary, we conclude that a network SPOOF will, in general, contain a large number of terms compared to that in a conventional Boolean expression for the network. However, that the SPOOF completely characterizes the topology as well as the function of a network (to be shown in Section 2.2) has consequences which, we believe, more than compensate for this drawback.

## Theorem 2.2

The expression obtained when all the path lists are removed from a network SPOOF is the Boolean network function, although not necessarily in reduced form.

## Proof

In constructing a SPOOF we follow all the rules of ordinary Boolean algebra, differing only in that we augment literals with path lists and omit normally-allowed simplifications. Hence removing the path lists gives an expression for the Boolean network function.

A second useful function obtainable directly from a SPOOF is the "E-expression", a Boolean expression in which "literal conflicts" of the type  $x\bar{x}$  and  $x+\bar{x}$  are preserved and no other algebraic simplification is performed. Klayton and Susskind have shown that complete multiple-fault-detection test-sets for stuck-at faults can be determined

from the E-expression for a network without considering fault patterns enumeratively [7]. Although we do not utilize E-expressions because we aim at a theory applicable to a variety of fault types, we include the following theorem for completeness.

## Theorem 2.3

The expression obtained when all the path lists are removed from a network SPOOF and no simplifications are performed is the E-expression for the network.

## Proof

This theorem follows immediately from Theorem 2.1 and the definition of E-expressions [7].

## Example 2.2

For the circuit of Fig. 1.2 the SPOOF was obtained in Example 2.1. Removing the path lists from the SPOOF, S<sub>8</sub>, gives the network E-expression:

$$E_8 = a\bar{b}b + a\bar{b}c + a\bar{b}d + \bar{b}\bar{c}\bar{d}$$

Also, the network Boolean function is

$$z = a\bar{b}b + a\bar{b}c + a\bar{b}d + \bar{b}c\bar{d}$$

=  $a\bar{b} + \bar{b}c\bar{d}$ .

It may be observed that, as a consequence of our leadlabeling convention, SPOOF terms can be compacted by eliminating path list entries of leads that fan out. For example, the path list 2,2b,5,5a,6,8 from Example 2.1 is unambiguously represented by 2b,5a,6,8. Henceforth we will write path lists in this compacted form, understanding, however, that the complete list is implied.

Readers familiar with the historical development of fault analysis will have recognized the similarity of the SPOOF to earlier algebraic notations by Poage and Armstrong. Specifically, a network function written in terms of Poage's "element propositions" [8] contains precisely the same information as the SPOOF, although Poage's notational form is cumbersome. On the other hand, Armstrong's "equivalent normal form" [9], which has the same form as the SPOOF, does not indicate inversion parity in its path lists, and this is a critical shortcoming.

## 2.2 Properties of SPOOF's

In this section we prove that the SPOOF defines the topology as well as the function of a logic network. Then we present theorems that are the basis of procedures for algebraically finding tests under a variety of fault models.

## Theorem 2.4

Given the output SPOOF of a gate, the function and input SPOOF's of the gate can be determined.

## Proof

Let G be the gate with output lead p for which the SPOOF  $_p^S$  is given. The last path list entry of every term of  $_p^S$  is p. Let  $_p^S$  be  $_p^S$  with p omitted from the path lists. Construct the set E consisting of the last entry in each path list of  $_p^S$ . Suppose  $_p^S$  Suppose  $_p^S$  is k or k. Then the inputs of G are  $_p^S$  is possible.

When G is a single-input gate and E={i} [E={ $\vec{i}$ }], then G is non-inverting [inverting], and S<sub>i</sub> is  $\hat{S}_p$  [( $\hat{S}_p$ )].

When G is a multi-input gate, either every product of  $\overset{\circ}{S}_p$  contains all the elements in E or every product contains a single distinct element in E. (This is because either  $\overset{\circ}{S}_p = S_1^* S_j^* \cdots S_m^*$  or  $\overset{\circ}{S}_p = S_1^* + S_j^* + \cdots + S_m^*$ . In the former case,  $\overset{\circ}{S}_p$  can be written as  $P_1 P_j \cdots P_m$ , where each  $P_k$  is a sum-of-products expression in which every term has last path entry  $k^*$ . In the latter case,  $\overset{\circ}{S}_p$  can be written as  $P_1 + P_j + \cdots + P_m$  with each  $P_k$  as above. Then G can be represented by an AND or an OR, respectively, with some number of inverting inputs. In either case, if keE [ $\bar{k}$ EE], then the corresponding input of G is non-inverting [inverting], and  $S_k$  is  $P_k$  [ $(\bar{P}_k)$ ].

## Theorem 2.5

Given a network SPOOF, the gate-level topology of the network and each of the internal lead SPOOF's can be reconstructed.

## Proof

Whenever we have the SPOOF for the output of a gate -- the common last path entry of every term is not a fanout branch -- we use Theorem 2.4 to determine the function and input SPOOF's of the gate. Whenever we have the SPOOF for a fanout branch, say  $S_q$ , then the SPOOF for the stem lead of q is  $S_q$ . Using these rules we work from the network output to the inputs, thus reconstructing the gate-level topology and each of the internal lead SPOOF's.

An ordinary Boolean output expression characterizes network behavior as a function of the primary input variables. However, in order to determine network behavior in the presence of some types of faults not of the stuck-at type, it is necessary to write the output expression as a function of input variables and certain lead variables. More precisely, we need the output function z in terms of the input variables and the lead variables  $y_1, y_j, \cdots, y_m$  corresponding to the leads  $i, j, \cdots, m$  of interest, treating each of these lead variables as an independent variable. Such an expression is the decomposition of z with respect to  $y_1, y_j, \cdots, y_m$ , which we denote as  $z[y_1, y_j, \cdots, y_m]$ . The SPOOF enables such functional decompositions to be obtained easily.

## Theorem 2.6

The decomposition  $z[y_1, y_1, \dots, y_m]$  corresponding to leads  $i, j, \dots, m$  can be determined from the network SPOOF  $S_z$  by the following procedure:

## Procedure 2.3

Suppose a term in the network SPOOF  $S_z$  has path list  $a^*,b^*,\cdots,z$ . If no lead in this list is a lead of decomposition, then simply remove the path list from the literal. If any leads in the list are leads of decomposition, let k be that decomposition lead closest to the network output (k\* appears after every other decomposition lead in the list). Then replace the term by  $y_k [\bar{y}_k]$  when k\* is unbarred [barred]. Applying this procedure to every term in  $S_z$  yields  $z[y_1,y_1,\cdots,y_m]$ .

#### Proof

Consider the SPOOF  $S_z$  obtained for a network Z' exactly like the given one Z, except that in Z' the leads i,j,...,m are made primary input leads driven by the independent variables  $y_i, y_j, \dots, y_m$ . Clearly, the output function z' of Z' is precisely the desired decomposition  $z[y_i, y_j, \dots, y_m]$ .

Any path J in Z that does not include a decomposition lead is duplicated in Z'. Consequently, each term  $x_J^\star$  in  $S_Z$  must be present in  $S_Z$ .

Any path K in Z that includes decomposition leads is broken in Z' at each decomposition lead. So the effect of input variable x due to path K on  $S_z$  is taken over by variable  $y_k$  in  $S_z$ , where k is that decomposition lead in K closest to the output. Consequently, for each term  $x_k^*$  in  $S_z$  there is a corresponding term  $(y_k^*)_L$  in  $S_z$ , where L is that part of K from  $k^*$  to the output. Furthermore, since a path entry  $k^*$  is unbarred [barred] when there is an even [odd] number of inversions from k to the output along path L, then  $y_k$  must be unbarred [barred] when  $k^*$  is unbarred [barred].

The given procedure follows precisely the above prescription, except that the path lists are removed so that z', instead of  $S_z'$ , is obtained.

#### Theorem 2.7

The output function  $z_F$  of a network when some pattern of stuck-at faults is present can be determined from the network SPOOF  $S_z$  by the following procedure:

#### Procedure 2.4

Suppose a term in  $S_Z$  has path list  $a^*,b^*,\cdots,z$ . If no lead in this list is faulted, then simply remove the path list from the literal. If any leads in the list are faulted, let k be that faulted lead closest to the network output (k\* appears after every other faulted lead in the list). Then if k is stuck-at-v, replace the term by  $v[\bar{v}]$  when k\* is unbarred [barred]. Applying this procedure to every term in  $S_Z$  yields  $z_F$ .

#### Proof

Let F be the fault  $i@v_i, j@v_j, \cdots, m@v_m$ . Clearly,  $z_F$  is  $z[y_i, y_j, \cdots, y_m]$  with  $y_i = v_i, y_j = v_j, \cdots, y_m = v_m$ . This is precisely the effect of Procedure 2.4.

#### Example 2.3

For the circuit of Fig. 1.2 the SPOOF was obtained in Example 2.1. Applying Procedure 2.3 to determine  $z[y_{5a}]$  gives

$$z[y_{5a}] = a\bar{b}y_{5a}^{+} + a\bar{b}y_{5a}^{+} + a\bar{b}y_{5a}^{+} + b\bar{c}\bar{d}$$

=  $a\bar{b}y_{5a}^{+} + b\bar{c}\bar{d}$

Applying Procedure 2.4 to determine z<sub>F</sub> for the fault 2b@0 gives

$$z_F = a\bar{b}0 + a\bar{b}c + a\bar{b}d + 1\bar{c}\bar{d}$$

=  $a\bar{b} + \bar{c}\bar{d}$

We note that Procedure 2.4 has previously been proved as Theorem 6.12 in [10] (also published as Theorem 6.1 in [11]), but by a completely different approach.

By making use of decomposition, an algebraic equation solutions to which are tests can always be formulated for any given fault. However, this equation usually depends on lead variables as well as input variables. In order to solve such an equation for actual test vectors, one must substitute the appropriate lead-variable functions expressed in terms of the input variables. Obtaining the necessary lead functions is another task easily accomplished when the network SPOOF is known.

#### Theorem 2.8

The function  $y_i$  for lead i can be determined from the network SPOOF  $S_z$  by the following procedure:

#### Procedure 2.5

- 1. Find some term  $x_J^*$  in  $S_Z$  that has i\* as a path entry. Call L that part of J from i\* to the output.

- 2. Suppose  $S_z = \sum_{i=1}^{\infty} P_i$ . If in a product  $P_i$  no term contains L, replace  $P_i$  by 0. If in a product  $P_i$  some term contains L, remove the path lists from all such terms, and replace by 1 the terms in  $P_i$  that do not contain L.

- 3. If the first entry of L is i  $[\bar{i}]$ , the resulting expression is  $y_i [\bar{y}_i]$ .

## Proof

Every term in  $S_z$  with a path entry i  $[\bar{i}]$  originates from  $S_i$   $[\bar{S}_i]$ , hence  $y_i$   $[\bar{y}_i]$ . Because  $S_z$  is in sum-of-products form, a product in  $S_z$  that is independent of i  $[\bar{i}]$  contributes true vertices to  $S_z$  that may not be present in  $S_i$   $[\bar{S}_i]$ . Such vertices are eliminated by

replacing these products by 0's. In a product dependent on i  $[\bar{i}]$ , the terms not containing i  $[\bar{i}]$  may make  $S_z$  false even though  $S_{\bar{i}}$   $[\bar{S}_{\bar{i}}]$  is true. Replacing these terms by 1's ensures that the expression obtained will be true whenever  $S_{\bar{i}}$   $[\bar{S}_{\bar{i}}]$  is true.

Because in constructing SPOOF's no algebraic simplifications are possible, the entirety of  $S_i$   $[\bar{S}_i]$  is present in  $S_z$  for every path from i to the output that has an even [odd] number of inversions. If there are k paths from i to the output with even [odd] inversion-parity, then simply considering the presence of i  $[\bar{i}]$  in terms produces the function  $y_i$   $[\bar{y}_i]$  k times. Such a procedure is correct, for the sum of k  $y_i$ 's  $[\bar{y}_i$ 's] is  $y_i$   $[\bar{y}_i]$ . The given procedure, by extracting  $y_i$   $[\bar{y}_i]$  from the terms due to a single path L, eliminates this algebraic redundancy.

## Example 2.4

For the circuit of Fig. 1.2, the SPOOF was obtained in Example 2.1. Applying Procedure 2.5 to determine  $y_{5a}$ , we select L=5a,6,8. Then

$$y_{5a} = 1 \cdot 1 \cdot b + 1 \cdot 1 \cdot c + 1 \cdot 1 \cdot d + 0$$

= b + c + d

#### CHAPTER 3

### USING SPOOF'S TO FIND TESTS FOR SEVERAL FAULT TYPES

In this chapter we show how one can use the SPOOF as the basis of algebraic techniques for finding tests for a variety of fault types. In particular, we give procedures that determine (1) all the test vectors for any given combination of stuck-at faults; (2) all the test vectors for any given regional fault, a fault that alters the function of some subnetwork in an arbitrary but specified manner; (3) all the test vectors for any given "logical" short circuit, an umintended connection between signal leads that behaves like an AND or OR; and (4) all the test vectors for any given shorted gate-input diode, a non-stuck-at fault exhibited by certain logic families.

## 3.1 The Boolean-Difference Method for Finding Tests for Stuck-at Faults

The most widely known algebraic method for finding tests is an application of the "Boolean difference". If z is a network output function and y is some lead variable, then the Boolean difference of z with respect of y is

$$\frac{dz}{dv} = z_0 \oplus z_1$$

where  $z_v$  is the <u>residue</u> of z at y=v (z evaluated with y=v) and  $\oplus$  is the "exclusive-OR" operator. (By definition,  $a \oplus b = a \bar{b} + \bar{a}b$ .) Sellers, Hsiao, and Bearnsen have shown that solutions of the equation  $y \frac{dz}{dy} = 1$  [ $\bar{y} \frac{dz}{dy} = 1$ ] are all the fault-detection tests for the fault y@0 [y@1] [12].

From the proof of Theorem 2.7, the residue  $z_v$  is precisely the function  $z_F$  for the fault yev. Thus given a network SPOOF, the Boolean difference  $\frac{dz}{dy}$  is readily obtained.

In order to solve the equation  $y^* \frac{dz}{dy} = 1$  for actual test vectors, one must know, besides  $\frac{dz}{dy}$ , the lead function y in terms of the primary input variables. This function is also easily obtained from the SPOOF by Procedure 2.5.

#### Example 3.1

For the circuit of Fig. 1.2 the SPOOF was obtained in Example 2.1. Let us determine tests for the faults 5a00 and 5a01.

Applying Procedure 2.4, we determine the residues required for the Boolean difference:

$$z_0 = a\bar{b}0 + a\bar{b}0 + a\bar{b}0 + \bar{b}\bar{c}\bar{d} = \bar{b}\bar{c}\bar{d}$$

$z_1 = a\bar{b}1 + a\bar{b}1 + a\bar{b}1 + \bar{b}\bar{c}\bar{d} = a\bar{b} + \bar{b}\bar{c}\bar{d}$

The Boolean difference is

$$\frac{dz}{dy_{5a}} = z_0 \oplus z_1 = (\bar{b}\bar{c}\bar{d}) \oplus (a\bar{b} + \bar{b}\bar{c}\bar{d})$$

$$= a\bar{b}c + a\bar{b}d$$

From Example 2.4 the lead function is

$$y_{5a} = b + c + d$$

Thus the stuck-at-0 tests are solutions of

$$y \frac{dz}{dy} = (b + c + d)(a\bar{b}c + a\bar{b}d)$$

$$= a\bar{b}c + a\bar{b}d = 1$$

There are three tests, namely the input vectors abcd = 1010, 1011, and 1001.

The stuck-at-1 tests are solutions of

$$\bar{y} \frac{dz}{dy} = (\bar{b}\bar{c}\bar{d})(a\bar{b}c + a\bar{b}d) = 1$$

This equation has no solutions, and the fault is undetectable.

It should be noted that when Boolean differences and lead functions are found from the SPOOF, there is no need to pre-store tables of functions, nor is reconvergent fanout a matter requiring special attention (cf. [13]).

Susskind has shown that the Boolean difference can be used to find fault-location tests as well as fault-detection tests: Solutions of the equation  $y_1^* \frac{dz}{dy_1} \oplus y_2^* \frac{dz}{dy_2} = 1$  are all the tests that distinguish the faults  $y_1^@v_1$  and  $y_2^@v_2$ , where  $y_i$  is unbarred [barred] when  $v_i^{=0}$  [ $v_i^{=1}$ ]. Susskind also described Boolean difference test generation for multiple faults [14]. In all cases, the necessary residues and lead functions can be found from the SPOOF.

## 3.2 The Direct-Difference Method for Finding Tests for Stuck-at Faults

If z is the intended output function of a network and  $z_F$  is its function when some fault F is present, then the fault-detection tests for F are all the input vectors that distinguish  $z_F$  from z, i.e., solutions of the equation  $z \neq z_F$ . As Even and Meyer have shown, the solutions of  $z \neq z_F$  are precisely the same as those of  $z \oplus z_F = 1$  [15]. We call  $z \oplus z_F$  the <u>direct difference</u>, since it is a "direct" expression of the necessary test conditions. When F is a stuck-at fault, both z

and  $z_F$  are readily obtained from the network SPOOF (by Theorem 2.2 and Procedure 2.4, respectively).

#### Example 3.2

For the circuit in Fig. 1.2 the SPOOF was obtained in Example 2.1. Let F be the fault 5a00. We find

$$z = a\bar{b} + \bar{b}\bar{c}\bar{d}$$

$$z_{F} = a\bar{b}0 + a\bar{b}0 + a\bar{b}0 + \bar{b}\bar{c}\bar{d} = \bar{b}\bar{c}\bar{d}$$

The tests are solutions of

$$z \oplus z_F = (a\bar{b} + \bar{b}\bar{c}\bar{d}) \oplus (\bar{b}\bar{c}\bar{d})$$

=  $a\bar{b}c + a\bar{b}d = 1$

This is the same equation as was found by the Boolean-difference method in Example 3.1. For the fault 5a@l,

$$z_F = a\bar{b}1 + a\bar{b}1 + a\bar{b}1 + \bar{b}\bar{c}\bar{d}$$

=  $a\bar{b} + \bar{b}\bar{c}\bar{d}$

The direct difference is

$$z \oplus z_F = (a\bar{b} + \bar{b}\bar{c}\bar{d}) \oplus (a\bar{b} + \bar{b}\bar{c}\bar{d}) = 0$$

Thus the equation z = 1 has no solutions, and as was concluded by the Boolean-difference method in Example 3.1, the fault is undetectable.

Defining the direct difference for fault-location tests is just as simple as it was for fault-detection tests: The tests that distinguish a fault F1 from a fault F2 are those input vectors for which  $z_{F1}$  and  $z_{F2}$  differ, i.e., solutions of the equation  $z_{F1}^{\oplus z}_{F2}=1$ .

Again, when F1 and F2 are stuck-at faults,  $z_{F1}$  and  $z_{F2}$  are readily obtained from the network SPOOF.

# 3.3 Comparison of the Boolean-Difference and Direct-Difference Methods

In this section we compare the Boolean-difference and direct-difference methods for finding tests. First we show that the two methods yield exactly the same results.

Consider tests for the fault ye0. Since z can always be written in the form  $z=\bar{y}z$   $\oplus yz_1$  and  $z_F=z_0$  for this fault, we have

$$z^{\bigoplus z}_{F} = (\bar{y}z_{0}^{\bigoplus y}z_{1}^{\bigoplus z_{0}})$$

$$= (1^{\bigoplus \bar{y}})z_{0}^{\bigoplus y}z_{1}$$

$$= yz_{0}^{\bigoplus y}z_{1}$$

$$= y(z_{0}^{\oplus z})$$

$$= y \frac{dz}{dy}$$

When the fault is yel, one similarly obtains  $z \oplus z_F = \bar{y} \frac{dz}{dy}$ . Thus for the case of fault detection, precisely the same set of tests is obtained by either method.

Now consider fault-location tests. Using the result just obtained, we have

$$y_1^* \frac{dz}{dy_1} \oplus y_2^* \frac{dz}{dy_2} = (z \oplus z_{F1}) \oplus (z \oplus z_{F2})$$

$$= z_{F1} \oplus z_{F2}$$

Again, the Boolean-difference and direct-difference expressions are equivalent.

Now we compare the computational effort required by the two methods. We assume for both cases that the network SPOOF has been found and that all required expressions are derived from it. Finding a fault-detection test by the Boolean-difference method requires the following:

- 1. Find the residues  $z_0$  and  $z_1$ .

- 2. Find the Boolean difference  $\frac{dz}{dy} = z_0 \oplus z_1$ .

- 3. Find the lead function y\*.

- 4. Form  $y^* \frac{dz}{dy}$ .

Finding a fault-detection test by the direct-difference method requires the following:

- 1. Find the fault function z<sub>F</sub>.

- 2. Form z Dz.

As was shown in Section 1.4, when y is the lead variable for an input to a multi-input gate, a test need be found for only one of the two possible stuck-at faults. Then the direct-difference method is clearly more efficient: Only one residue  $(z_F)$  has to be determined, and finding the lead function is obviated.

When y is the lead variable for a lead that is not a gate input, tests need be found for both of the possible stuck-at faults. Then the required computational efforts are about the same. Thus using the direct-difference method can only result in computational savings, the advantage being dependent on the actual gate-level

circuit configuration. Comparing the two methods for the case of fault-location tests yields the same conclusion.

It is appropriate to note here that the complexity of computing exclusive-OR's can be greatly reduced by employing the following identity:

$$(a+b)\Phi(a+c) = \bar{a}(b\Phi c)$$

In calculating a direct difference  $z \oplus z_F$ , for example, any product independent of the faulty leads will be present in both z and  $z_F$ , and the complement of the sum of all such products can be "factored out" of the exclusive-OR.

## 3.4 Finding Tests for Regional Faults

A fault that alters the logic function of some subnetwork in an arbitrary but specified manner will be called a <u>regional fault</u>. For example, the accidental insertion of a NOR gate in place of a NAND is a regional fault. When the network SPOOF is known, the tests that detect a given regional fault can be found by the following procedure:

## Procedure 3.1

Let the region (subnetwork) of interest have input leads i,j,...,m and output lead p. Suppose fault F causes the function of  $y_p$  on lead p to be  $y_{pF} = f(y_1, y_j, \dots, y_m)$ . From the network SPOOF determine  $y_1, y_j, \dots, y_m$  in terms of primary input variables and the decomposition of the network output function  $z[y_p]$ . Then  $z_F$  is  $z[y_p]$  with  $y_{pF}$ , expressed in terms of primary input variables, substituted for  $y_p$ . Tests are solutions of the equation  $z \oplus z_F = 1$ .

#### Example 3.3

In the circuit of Fig. 1.2, suppose the gate with output lead 6 behaves as a majority gate. Then the region-function in the presence of the fault is

$$y_{6F} = maj(y_1, y_{2a}, y_{5a}) = y_1y_{2a} + y_1y_{5a} + y_{2a}y_{5a}$$

From the network SPOOF (Example 2.1)

$$y_1 = a$$

$$y_{2a} = b$$

$$y_{5a} = b + c + d$$

and

$$z[y_6] = y_6 + \overline{b}\overline{c}\overline{d}$$

Thus

$$y_{6F} = ab + a(b+c+d) + b(b+c+d)$$

$$= b + ac + ad$$

$$z_F = b + ac + ad + \overline{b}\overline{c}\overline{d}$$

$$= a + b + \overline{c}\overline{d}$$

Tests for F are solutions of

$$z \oplus z_{\mathbf{F}} = (a\bar{b} + b\bar{c}\bar{d}) \oplus (a + b + \bar{c}\bar{d}) = b = 1$$

Regional faults are very general in nature, including for example, stuck-at faults as a subclass. Procedure 3.1 can be used to find tests in all cases; however, procedures "tailored" to more specific fault types are generally more efficient.

Susskind has described test generation for arbitrary single-gate regional faults by a Boolean-difference method [14]. We

expect that the direct-difference formulation has a small computational advantage over that technique.

## 3.5 Finding Tests for Short Circuits

A <u>short circuit</u> is an unintended connection between signal leads in a network. It is likely that short circuits comprise the largest and most commonly-occurring class of faults not detected by tests designed specifically for single stuck-at faults.

Whereas stuck-at faults have the effect of simplifying the logic topology (some connections and even entire gates are effective-ly eliminated), short-circuits complicate the topology (connections and "gates" are introduced). It is possible, for example, that these new connections produce a loop in a normally loop-free network, and these loops complicate test generation because they can make circuit operation sequential. Because the SPOOF contains at least one term for each complete network path, such occurrences are easily identified: Suppose the short circuit is between leads i and j. Then a cycle is indicated if any path list has both i\* and j\* as entries. Although we exclude cycle-causing faults from consideration at this time, that we easily identify these cases is of some importance, for at least it is then known which faults must be treated by more sophisticated techniques.

Because our basis for network analysis is a <u>logical</u> model, we can characterize faults only in terms of their <u>logical</u> effect.

Thus, we assume that a short circuit can be modeled as a wired-logic

AND or OR at the site of the connection. This assumption is usually

valid for logic families with passive output pull-up or pull-down (RTL, DTL, ECL), but may be questionable for families with active pull-up and pull-down (TTL). (For families like TTL perhaps tests should be found to cover both assumptions.)

Tests for short-circuit faults that do not introduce cycles are obtained as follows:

#### Procedure 3.2

Suppose F is the fault that causes leads i and j to be \*-shorted (\* denotes either AND or OR). If i or j is a fan-out branch, represent it by the gate output or primary input that drives it. (This accounts for "backward" propagation of signals.) Use the network SPOOF to determine the lead functions  $y_i$  and  $y_j$  and the decomposition of the network function  $z[y_i,y_j]$ . Then  $y_{iF} = y_{jF} = y_i * y_j$ , and  $z_F$  is  $z[y_i,y_j]$  with  $y_{iF}$  and  $y_{jF}$ , expressed in terms of the primary inputs, substituted for  $y_i$  and  $y_j$ . Again, solutions of  $z\Phi z_F = 1$  are the tests for F.

## Example 3.4

In the circuit of Fig. 1.2, suppose leads 1 and 7 are AND-shorted. From the network SPOOF (Example 2.1), this fault does not cause a cycle. Then

$$y_1 = a$$

$$y_7 = \bar{b}\bar{c}\bar{d}$$

$$z[y_1,y_7] = y_1\bar{b}b + y_1\bar{b}c + y_1\bar{b}d + y_7y_7y_7 = y_1\bar{b}c + y_1\bar{b}d + y_7$$

$$y_{1F} = y_{7F} = y_1 \cdot y_7 = a\bar{b}\bar{c}\bar{d}$$

$z_F = a\bar{b}\bar{c}d\bar{b}c + a\bar{b}\bar{c}d\bar{b}d + a\bar{b}\bar{c}\bar{d} = a\bar{b}\bar{c}\bar{d}$   $z\Phi z_F = (a\bar{b}+\bar{b}\bar{c}\bar{d}) \oplus (a\bar{b}\bar{c}\bar{d}) = a\bar{b}c + a\bar{b}d + \bar{a}\bar{b}\bar{c}\bar{d}$

Input combinations 1010, 1011, 1001, and 0000 are tests for this fault.

### 3.6 Finding Tests for Shorted Gate-Input Diodes

The last type of fault to be considered is shorts in gate-input diodes, a failure mode of certain logic families such as DTL. Shorted input-diode faults have been studied by Chang in connection with fault simulation [16]. We assume networks composed of all NAND or all NOR gates from the same logic family, although our method can be applied in other cases as well.

To see how shorted gate-input diodes affect a network, consider the state of the circuit of Fig. 3.1 when a=1 and b=0. When the network is realized using DTL gates as illustrated in Fig. 3.2 and the diode for lead la (Fig. 3.1) is shorted, the input to the inverter (lead lb) is a logic 0 instead of a 1. That is, the AND-ed level, usually blocked by the diode, "backward propagates" onto lead lb. For a nominal b=0 voltage level of  $v_{CE}$ , the level at the input to the inverter is  $v_{CE}^{+}v_{BE}$  (the gate input voltage plus the voltage drop across the non-shorted input-diode), which is well below its threshold voltage of  $2v_{BE}$ . Observe that the output of the faulty gate is completely unaffected by the fault, and in Fig. 3.1 the fault can affect the network output only by virtue of the path through the inverter, i.e., the fanout on lead 1. In general, unless the input lead to the shorted diode is a fanout branch, the fault is of no consequence at all.

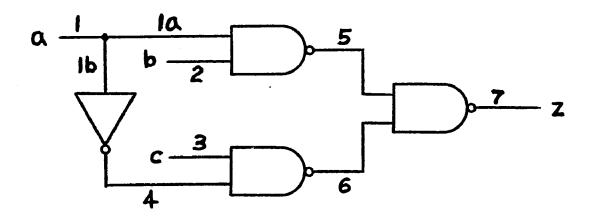

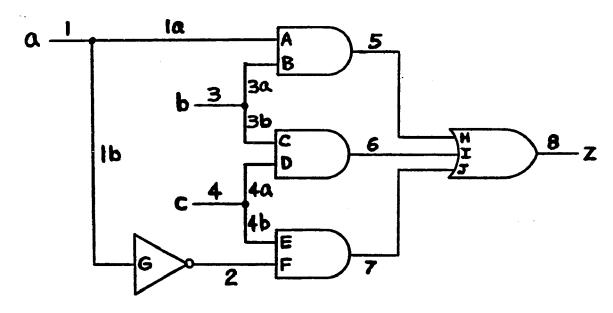

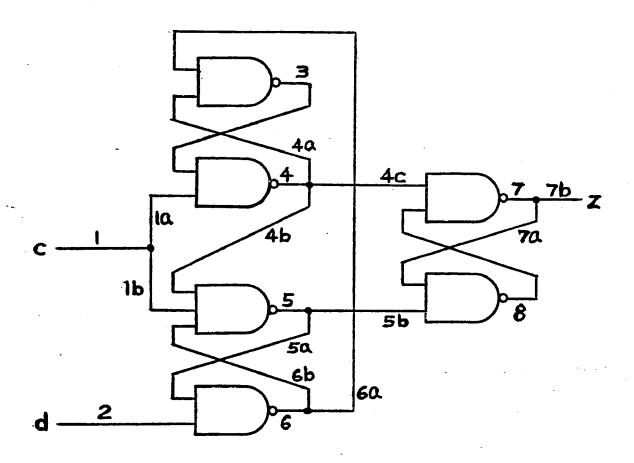

Figure 3.1. Circuit to illustrate the effect of a shorted gate-input diode fault.

Figure 3.2 Typical DTL gate (shown is Motorola MC946).

In light of the preceding discussion, it follows that tests for shorted gate-input diodes are obtained as follows:

#### Procedure 3.3