The Preserve: Lehigh Library Digital Collections

# The Scaling Of Submicron Cmos Devices.

#### Citation

Tran, Conn-Luan. The Scaling Of Submicron Cmos Devices. 1990, https://preserve.lehigh.edu/lehigh-scholarship/graduate-publications-theses-dissertations/theses-dissertations/scaling.

Find more at https://preserve.lehigh.edu/

#### INFORMATION TO USERS

The most advanced technology has been used to photograph and reproduce this manuscript from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

**U·M·I**

#### Order Number 9109586

## The scaling of submicron CMOS devices

Tran, Conn-Luân, Ph.D. Lehigh University, 1990

| <del>-</del> |  |  |

|--------------|--|--|

# The Scaling of Submicron CMOS Devices

by Conn-Luân Tran

A Dissertation

Presented to the Graduate Committee

of Lehigh University

in Candidacy for the Degree of

Doctor of Philosophy

in

Electrical Engineering

Lehigh University

1990

### **Certificate of Approval**

This dissertation is approved and recommended for acceptance in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

September 26, 1990

Date

Prof. M.H. White

Dissertation Advisor

Dissertation Committee

Prof. M. H. White (Chairman)

Prof. M. K. Hatalis

Dr. D. S. Yaney-

Prof. D. R. Young

#### **ACKNOWLEDGEMENTS**

I wish to express my grateful thanks to Prof. Marvin H. White, for his guidance, suggestions and tolerance during the course of this research. Special thanks are due to the committee members, Prof. Miltiadis Hatalis, Dr. Dave Yaney and Prof. Donald Young for recommendation to focus on the dissertation topics. The late Prof. Frank Feigl, who served as a committee member during my general examination, is respectfully remembered. The encouragement and support from the management at AT&T Bell Laboratories, Drs. Pete Panousis. Dinesh Mehta, Dan McGillis, Morgan Thoma, Jorge Agraz-Guerena are deeply appreciated. A special acknowledgement is due to Dr. Robert Ashton, my long time officemate, for his encouragement, allowing me to use of his several useful measurement subroutines, and timely proof-reading chapters of this dissertation. Collaboration with Technology CAD colleagues in device simulation, B. Meinerzhagen, J. Prendergast, W. Lui, and H. Dirks are greatly appreciated. Technical discussions, encouragement and sometimes a push by my colleagues and friends at Lehigh University and AT&T are fondly remembered. Among them, Cris Lawrence, Nancy Minor, Jane Swiderski, Felicia Herring, Daniel Chesire, Mike Kelly, Richard Booth, Tom Krutsick, Richard Siergiej. Members of the BiCMOS Groups, Tom Ham, Sue Vitkavage, John Osenbach, and Don Dennis gave supporting boost during the final weeks of this writing. Thanks are due to my brothers, Luan Q. and Luong, who did the figures during the various phases of the manuscript preparation. My dear friend, Dr. BichVan Phan, whose daily encouragement from a long distance is heartedly appreciated. Support from my family members and loved ones has been the main thrust for my endeavor, and to that, this work is especially dedicated to my parents and grandparents.

I am greatly appreciate to the AT&T Bell Laboratories Graduate Study Program for the financial support of this doctoral program.

#### **CONTENTS**

| AE  | STRACT                                                                   | 1          |

|-----|--------------------------------------------------------------------------|------------|

| Ch  | apter 1                                                                  | 3          |

| IN  | TRODUCTION                                                               | 3          |

| 1.1 | HISTORICAL REVIEW                                                        | 3          |

|     | 1.1.1 Major Inventions And Breakthroughs in Device Structures and Theory | 4          |

|     | 1.1.1.1 The Bipolar Transistor                                           | 4          |

|     | 1.1.1.2 The Field Effect Transistor Concepts                             | 5          |

|     | 1.1.1.3 Integrated Circuits Inventions                                   | $\epsilon$ |

|     | 1.1.2 Technological Breakthroughs                                        | 7          |

|     | 1.1.3 Circuit and System Applications Driven Technology                  | 9          |

| 1.2 | DEVELOPMENTS IN MOS LSI                                                  | 12         |

|     | 1.2.1 PMOS and NMOS Technologies                                         | 13         |

|     | 1.2.2 CMOS Technology                                                    | 13         |

|     | 1.2.2.1 Single Well CMOS                                                 | 14         |

|     | 1.2.2.2 Twin-Tub CMOS Technology                                         | 17         |

| 1.3 | DEVICE SCALING ASPECTS                                                   | 18         |

|     | 1.3.1 Constant Field Device Scaling                                      | 19         |

|     | 1.3.2 Practical Scaling of CMOS Devices                                  | 20         |

|     | 1.3.3 High Field Effects                                                 | 20         |

| 1.4 | SCOPE AND ORGANIZATION OF THE DISSERTATION                               | 22         |

|     | 1.4.1 Organization                                                       | 23         |

|     | 1.4.2 Contributions of this Work toward the Art                          | 24         |

| Cha | apter 2                                                                  | 27         |

| SU  | BMICRON CMOS DEVICE THEORY                                               | 27         |

| 2.1 | Introduction And Convention                                              | 27         |

| 2.2 | Subthreshold Conduction in a Long Channel MOSFET                         | 28         |

| 2.3 | Charge Sharing and Subthreshold Conduction in a Short Channel MOS Device | 38         |

| 2.4 | Threshold Voltage                                                        | 45         |

| 2.5 | Linear Drain Current                                                     | 47         |

| 2.6 | Saturation Regime                                                        | 48         |

| Cha | pter 3                                                                   | 51         |

| DE' | VICE DESIGN and PROCESS INTEGRATION                                      | 51         |

| 3.1 | INTRODUCTION                                                             | 51         |

| 3.2 | APPLICATIONS DRIVEN DEVICE DESIGN                                        | 51         |

|     | 3.2.1 Define the Circuit/System Applications of The Technology           | 51         |

|     | 3.2.2 Subthreshold Leakage Requirements                                  | 52         |

| 3 3 | PROCESSING TECHNOLOGY ASSESSMENT                                         | 53         |

|     | 3.3.1 Lithography Capability                        | 53 |

|-----|-----------------------------------------------------|----|

|     | 3.3.2 Pattern Transfer                              | 54 |

|     | 3.3.3 Isolation processes                           | 54 |

|     | 3.3.4 Other Processing Capabilities                 | 55 |

|     | 3.3.5 Local and Global Interconnect                 | 55 |

| 3.4 | DEVICE STRUCTURE DETERMINATION                      | 56 |

|     | 3.4.1 Gate Dielectric Material                      | 56 |

|     | 3.4.2 Gate Electrode Material Considerations        | 57 |

|     | 3.4.3 S/D Junction Formation                        | 57 |

| 3.5 | PRACTICAL DEVICE DESIGN CONSIDERATIONS              | 57 |

|     | 3.5.1 Polysilicon Gate Doping                       | 58 |

|     | 3.5.2 Minimum and Nominal Gate Length               | 60 |

|     | 3.5.3 Gate Oxide Thickness                          | 60 |

|     | 3.5.4 Off Current                                   | 60 |

|     | 3.5.5 Threshold Voltages                            | 61 |

|     | 3.5.6 Channel Doping and Body Effect Considerations | 61 |

|     | 3.5.7 Source & Drain Structure                      | 61 |

| 3.6 | DRAIN ENGINEERING                                   | 63 |

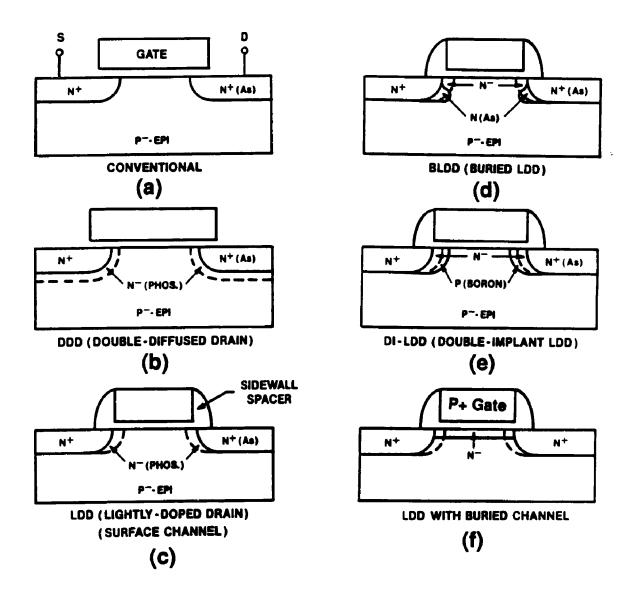

|     | 3.6.1 Conventional Drain                            | 64 |

|     | 3.6.2 Double Diffused Drain (DDD)                   | 64 |

|     | 3.6.3 Lightly Doped Drain (LDD)                     | 64 |

|     | 3.6.4 Variations of LDD                             | 65 |

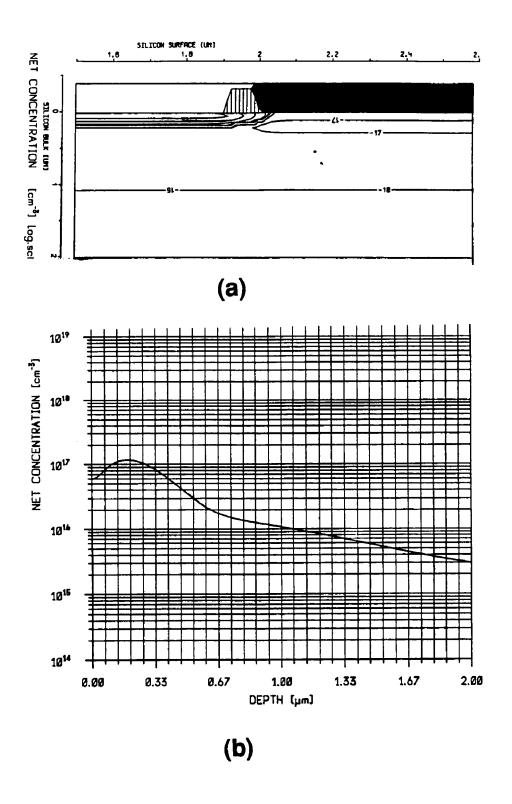

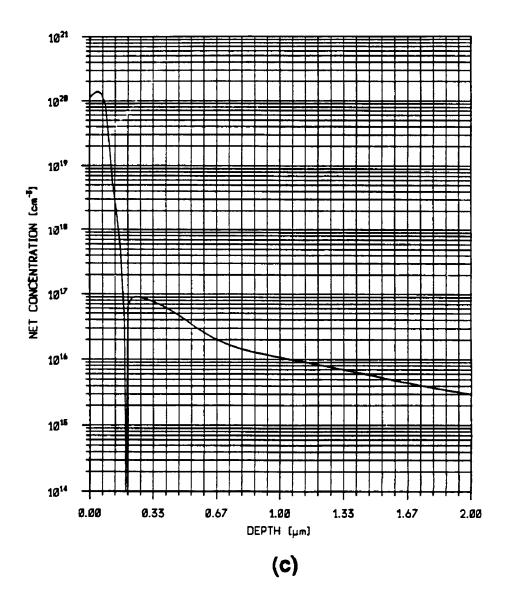

| 3.7 | PROCESS AND DEVICE SIMULATION                       | 66 |

|     | 3.7.1 BICEPS Process Simulator                      | 67 |

|     | 3.7.2 Device Simulation                             | 67 |

| 3.8 | DEVICE DESIGN USING PROCESS AND DEVICE SIMULATORS   | 74 |

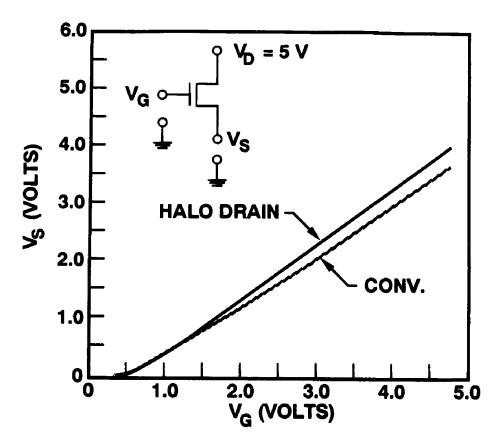

|     | 3.8.1 Low Body Effect NMOS Using Halo Drain         | 74 |

|     | 3.8.2 P-Channel Halo-Drain                          | 77 |

| 3.9 | SUMMARY                                             | 79 |

| Cha | pter 4                                              | 81 |

| CM  | OS FABRICATION PROCESS                              | 81 |

| 4.1 | INTRODUCTION                                        | 81 |

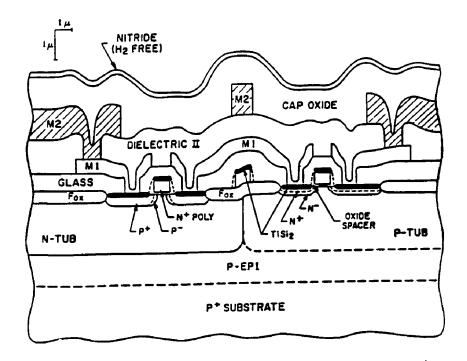

| 1.2 | TWIN-TUB CMOS FABRICATION SEQUENCE                  | 81 |

| 1.3 | FABRICATION PROCESS                                 | 83 |

|     | 4.3.1 Starting Material and Tub Formation           | 83 |

|     | 4.3.2 Active Area Definition                        | 86 |

|     | 4.3.3 Gate Oxide Process                            | 86 |

|     | 4.3.4 Gate Patterning                               | 88 |

|       | 4.3.5 Source and Drain Formation                                  | 88  |  |  |  |  |

|-------|-------------------------------------------------------------------|-----|--|--|--|--|

|       | 4.3.6 Self-Align Silicide (Salicide)                              | 90  |  |  |  |  |

|       | 4.3.7 First Level Dielectric and Metal                            | 92  |  |  |  |  |

| Ch    | Chapter 5                                                         |     |  |  |  |  |

| TE    | CHNOLOGY CHARACTERIZATION                                         | 95  |  |  |  |  |

| 5.1   | INTRODUCTION                                                      | 95  |  |  |  |  |

| 5.2   | PROCESS CHARACTERIZATION                                          | 96  |  |  |  |  |

|       | 5.2.1 Doping Profiles                                             | 96  |  |  |  |  |

|       | 5.2.2 Analytical Tools for Material and Structural Analysis       | 98  |  |  |  |  |

|       | 5.2.3 C-V Techniques for MOS Structure Characterization           | 98  |  |  |  |  |

|       | 5.2.4 Resistivity                                                 | 103 |  |  |  |  |

| 5.3   | DEVICE INTEGRITY IN SUBTHRESHOLD                                  | 104 |  |  |  |  |

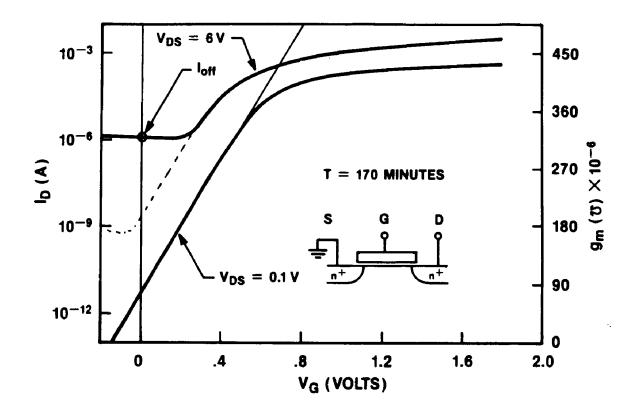

|       | 5.3.1 Subthreshold Conduction: The g Curves                       | 104 |  |  |  |  |

|       | 5.3.2 Reverse Subthreshold Swing                                  | 107 |  |  |  |  |

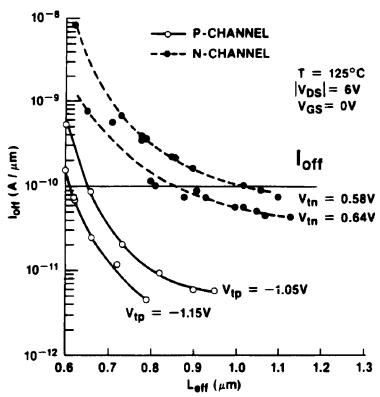

|       | 5.3.3 <i>l<sub>off</sub></i> Optimization                         | 108 |  |  |  |  |

| 5.4   | ACTIVE DEVICE PARAMETERS                                          | 110 |  |  |  |  |

|       | 5.4.1 Threshold Voltage                                           | 110 |  |  |  |  |

|       | 5.4.2 Reverse Short Channel Effects in Threshold Voltage          | 110 |  |  |  |  |

|       | 5.4.3 Transconductance and Linear Gain                            | 112 |  |  |  |  |

|       | 5.4.4 Effective Channel Length And Source-Drain Series Resistance | 115 |  |  |  |  |

|       | 5.4.5 Saturation Mode, and I <sub>on</sub>                        | 117 |  |  |  |  |

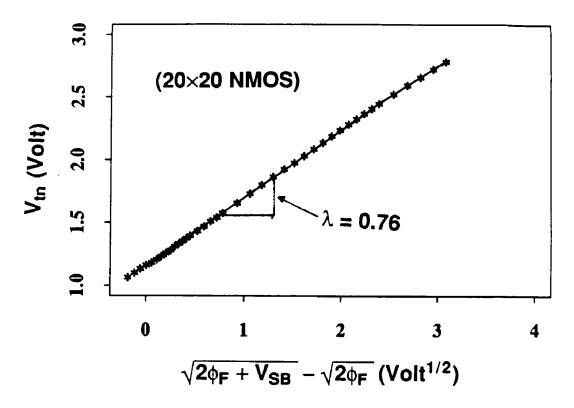

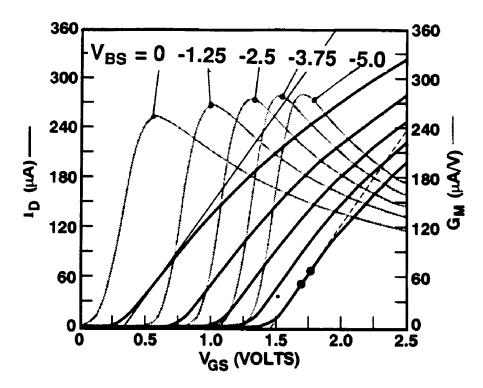

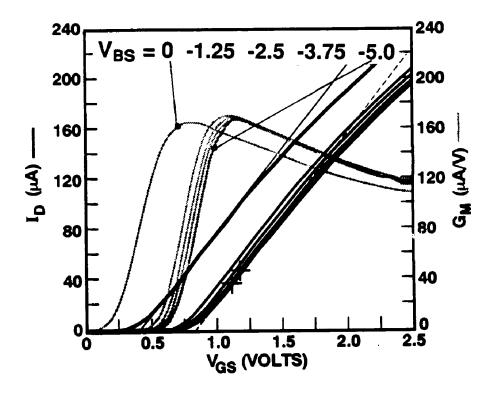

|       | 5.4.6 Body Effects and Channel Doping Profile                     | 118 |  |  |  |  |

| 5.5   | PARASITIC CHARACTERIZATION                                        | 122 |  |  |  |  |

|       | 5.5.1 Junction Leakage                                            | 122 |  |  |  |  |

|       | 5.5.2 Junction Capacitance                                        | 122 |  |  |  |  |

|       | 5.5.3 Isolation Leakage                                           | 123 |  |  |  |  |

| 5.6   | SUMMARY                                                           | 125 |  |  |  |  |

| Cha   | apter 6                                                           | 127 |  |  |  |  |

| НО    | T CARRIER GENERATION                                              | 127 |  |  |  |  |

| IN S  | SHORT CHANNEL MOS TRANSISTORS                                     | 127 |  |  |  |  |

| 6.1   | INTRODUCTION                                                      | 127 |  |  |  |  |

| 6.2   | HOT CARRIER GENERATION AND INJECTION MECHANISMS                   | 127 |  |  |  |  |

|       | 6.2.1 Channel Electric Field                                      | 129 |  |  |  |  |

|       | 6.2.2 Substrate Current                                           | 130 |  |  |  |  |

|       | 6.2.3 Analytical Model for Gate Current                           | 135 |  |  |  |  |

|       | 6.2.4 Numerical Simulation of Substrate and Gate Currents         | 138 |  |  |  |  |

| 6.3   | SUBSTRATE AND GATE CURRENTS OF LDD AND DDD NMOS TRANSISTORS       | 139 |  |  |  |  |

| 6.4   | DRAIN-SOURCE BREAKDOWN VOLTAGE                                    | 139 |  |  |  |  |

| · · · |                                                                   | 171 |  |  |  |  |

| 6.5 | SUMMARY                                                                     | 143 |

|-----|-----------------------------------------------------------------------------|-----|

| Ch  | apter 7                                                                     | 145 |

| CM  | IOS DEVICE AGING BY HOT CARRIER INJECTION                                   | 145 |

| 7.1 | INTRODUCTION                                                                | 145 |

| 7.2 | DEVICE AGING EXPERIMENTS AND OBSERVATIONS                                   | 145 |

|     | 7.2.1 Experimental Set-up                                                   | 145 |

|     | 7.2.2 Observations •                                                        | 146 |

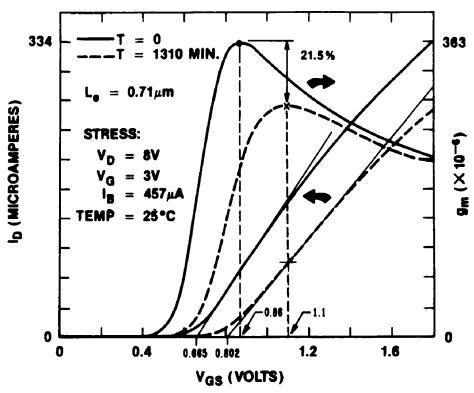

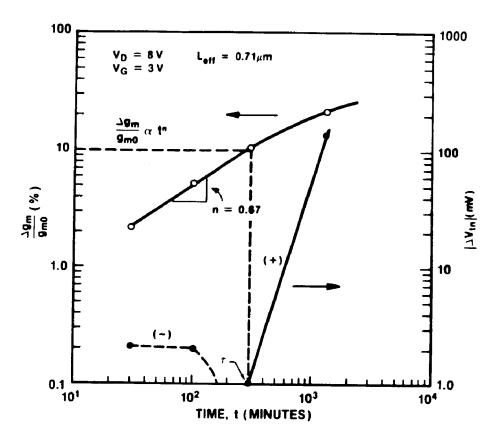

|     | 7.2.3 $g_m$ and $V_l$ Changes                                               | 150 |

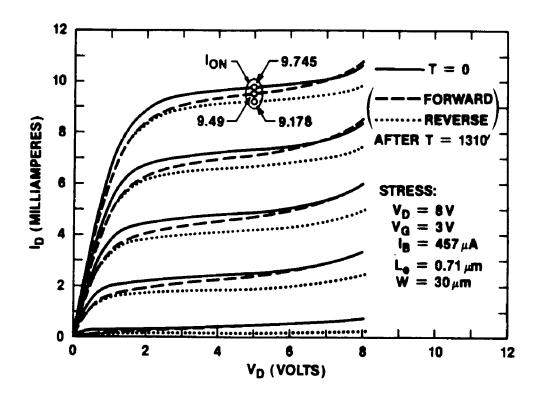

|     | 7.2.4 Changes in Saturation Characteristics                                 | 150 |

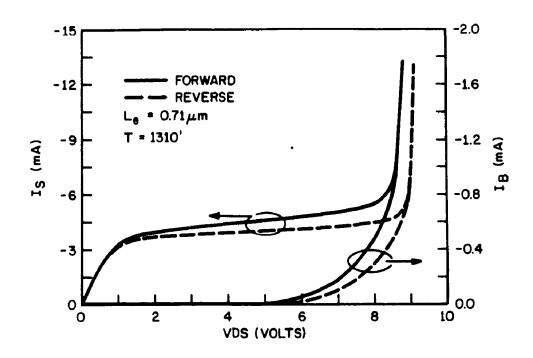

|     | 7.2.5 Hot Carrier Induced Drain Junction Leakage                            | 151 |

| 7.3 | THE ANALYSIS AND MODELING OF HOT CARRIER AGING MECHANISMS                   | 152 |

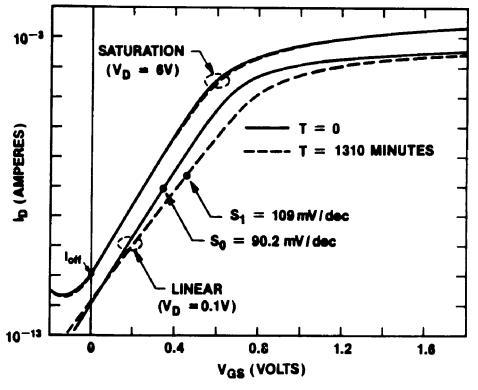

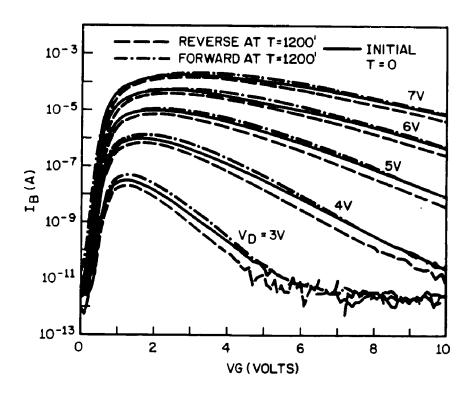

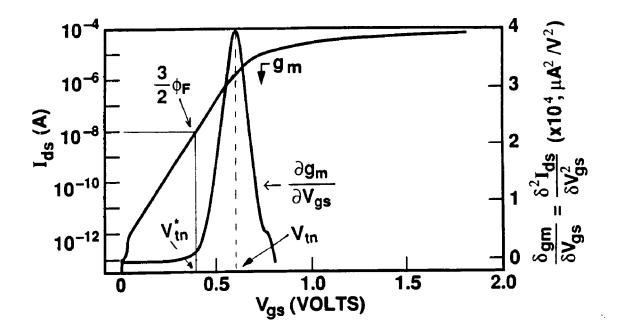

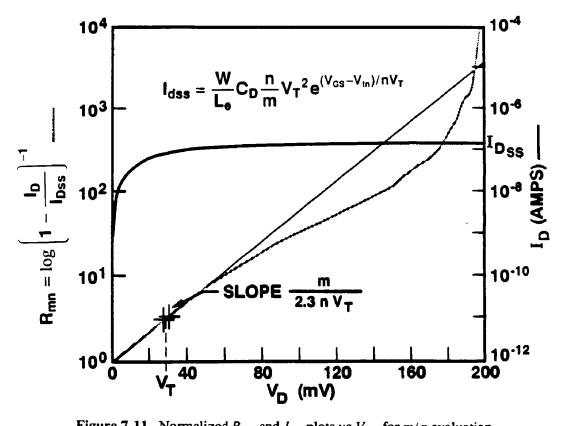

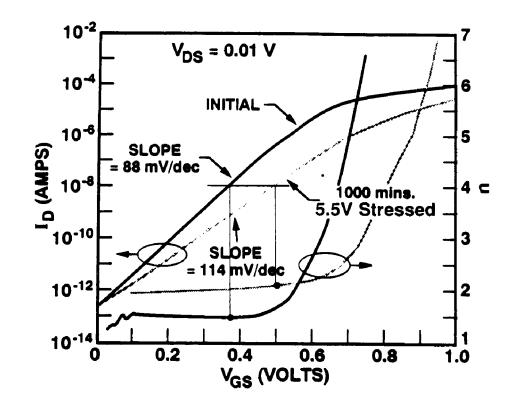

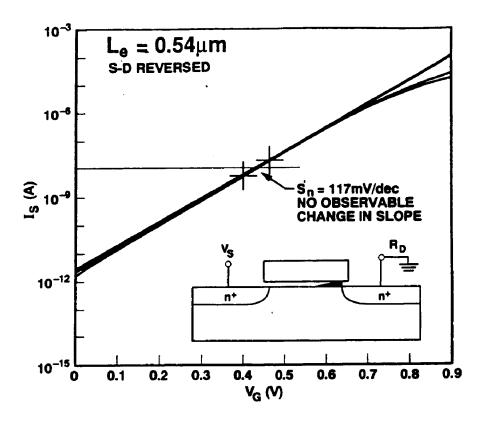

|     | 7.3.1 Subthreshold Current and Interface Trap Density                       | 155 |

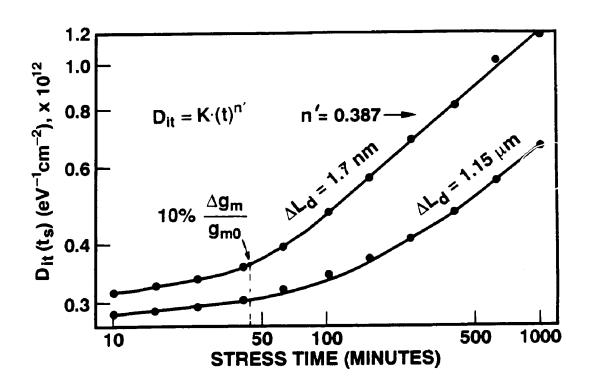

|     | 7.3.2 Determine Parameters n and m                                          | 157 |

|     | 7.3.3 Spatial Distribution of Interface State Density By Hot Carrier Stress | 159 |

|     | 7.3.3.1 Varying Back Gate Voltage                                           | 161 |

|     | 7.3.3.2 Varying Drain-to-Bulk Bias                                          | 162 |

|     | 7.3.4 Formulation of the Lateral Interface Trap Density                     | 163 |

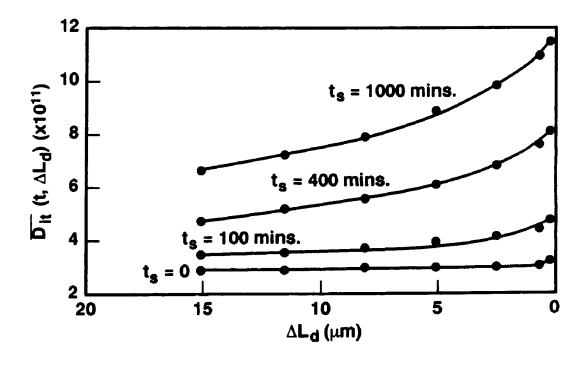

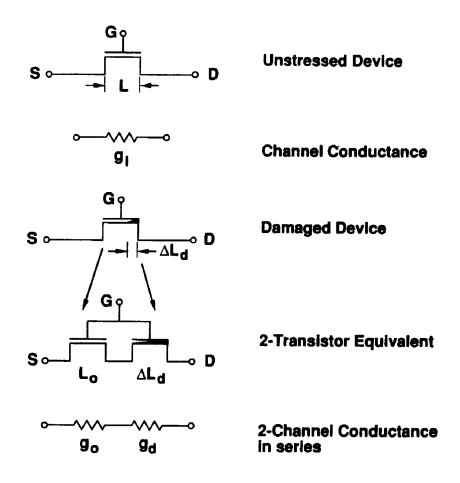

| 7.4 | THE VALIDITY OF TWO-TRANSISTOR EQUIVALENT MODEL FOR A DAMAGED DEVICE        | 166 |

|     | 7.4.1 Transconductance Degradation as a Function of Channel Length          | 169 |

| 7.5 | THE LIFETIME ANALYSIS                                                       | 172 |

| 7.6 | SUBSTRATE CURRENT IN A CMOS INVERTER AND CIRCUIT AGING                      | 177 |

| 7.7 | DISCUSSIONS                                                                 | 180 |

| 7.8 | SUMMARY                                                                     | 182 |

| Cha | pter 8                                                                      | 183 |

| ΑD  | VANCED TOPICS and FUTURE WORKS                                              | 183 |

| 8.1 | ISOLATION                                                                   | 183 |

|     | 8.1.1 Drawbacks of Conventional LOCOS                                       | 183 |

|     | 8.1.2 PBL Structure                                                         | 184 |

|     | 8.1.2.1 Field Oxide Thinning in Narrow Space                                | 186 |

| 8.2 | BiCMOS                                                                      | 187 |

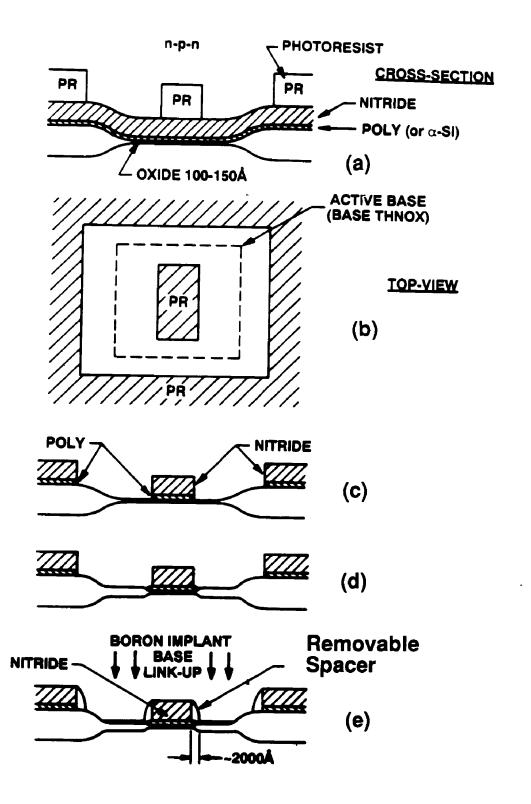

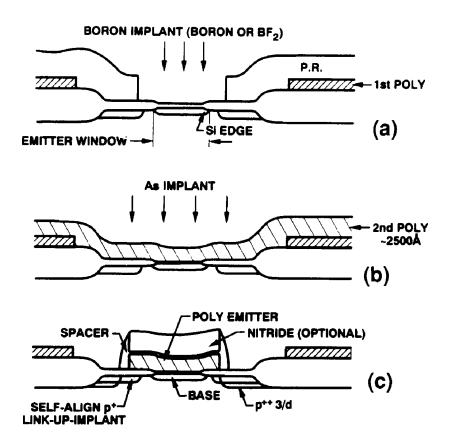

|     | 8.2.1 High Performance BiCMOS Fabrication Process                           | 188 |

|     | 8.2.1.1 Buried Layer                                                        | 188 |

|     | 8.2.1.2 Tub Formation                                                       | 189 |

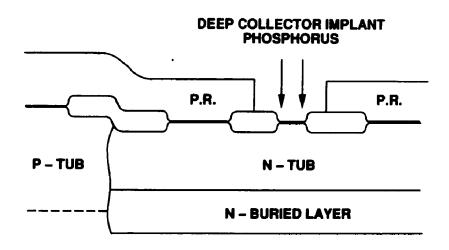

|     | 8.2.1.3 Deep Collector Implant                                              | 189 |

|     | 8.2.1.4 CMOS Gate Oxide Process                                             | 191 |

|     | 8.2.1.5 Base Definition                                                     | 191 |

|     | 8.2.2 Emitter Formation                                                     | 193 |

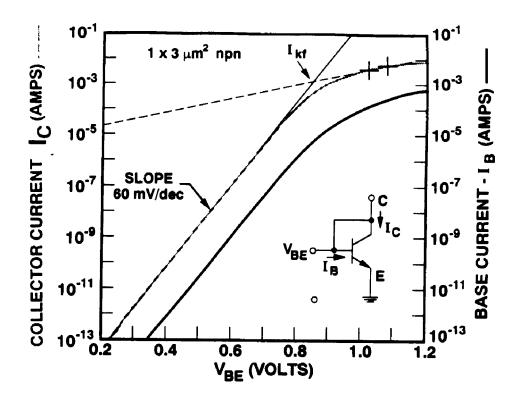

| 8.2.3 Bipolar Transistor Characteristics      | 193 |

|-----------------------------------------------|-----|

| 8.3 GATE DIELECTRIC MATERIAL                  | 197 |

| 8.4 LOCAL INTERCONNECTS & RAISED SOURCE/DRAIN | 198 |

| 8.5 OTHER RELIABILITY ISSUES                  | 199 |

| 8.6 SUMMARY                                   | 200 |

| Chapter 9                                     | 201 |

| CONCLUSIONS And RECOMMENDATIONS               | 201 |

| REFERENCES                                    |     |

| VITA                                          | 209 |

#### LIST OF FIGURES

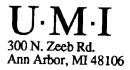

| Figure 1-1.  | Cross-Section of a MOS Transistor                                                                                                                                                                    | 6  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

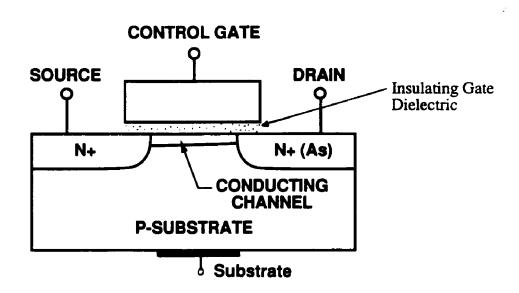

| Figure 1-2.  | DRAM and SRAM density vs the year of introduction.                                                                                                                                                   | 10 |

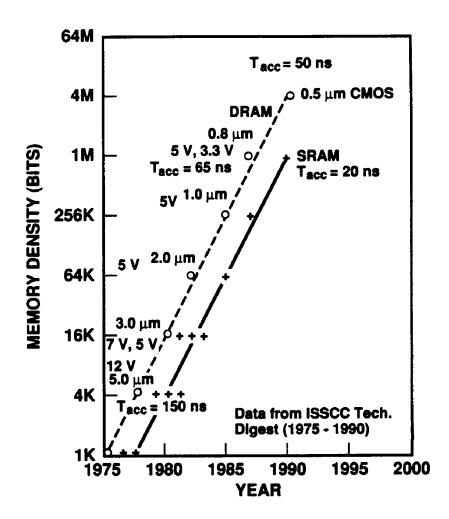

| Figure 1-3.  | Power-Delay Product per inverter gate versus year.                                                                                                                                                   | 11 |

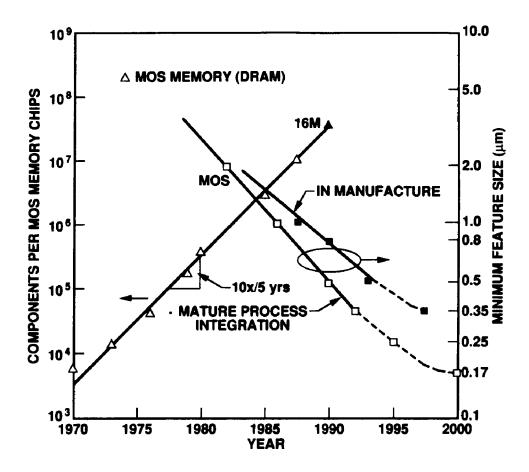

| Figure 1-4.  | MOS memory component growth and feature size reduction vs calendar year                                                                                                                              | 12 |

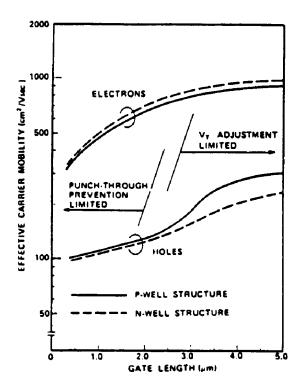

| Figure 1-5.  | Electrons and Holes Mobility on n- and p-well CMOS devices. [41]                                                                                                                                     | 15 |

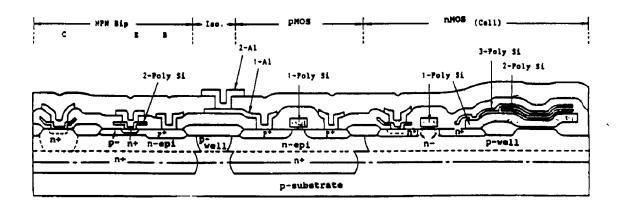

| Figure 1-6.  | n-well BiCMOS structure for SRAM application. <sup>[42]</sup>                                                                                                                                        | 16 |

| Figure 1-7.  | Cross section structure of a twin-tub CMOS structure. <sup>[43]</sup>                                                                                                                                | 17 |

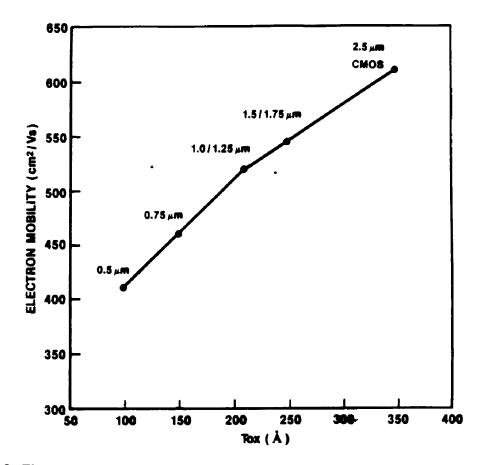

| Figure 1-8.  | Electron mobility versus gate oxide thickness for different CMOS Technologies with appropriate channel doping, (measured at peak transconductance of long channel devices, with $V_{DS}$ =0.1 $V$ ). | 21 |

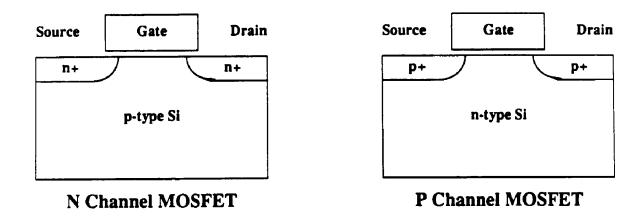

| Figure 2-1.  | Cross-Sections of n and p-channel MOS Transistors                                                                                                                                                    | 28 |

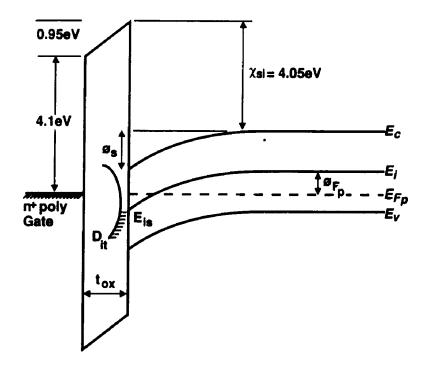

| Figure 2-2.  | Energy Band Diagram of Poly Gate MOS structure.                                                                                                                                                      | 29 |

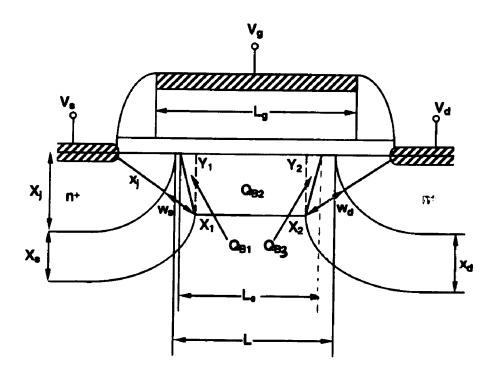

| Figure 2-3.  | Cross Section of a short channel MOS device with charge sharing boundary                                                                                                                             | 38 |

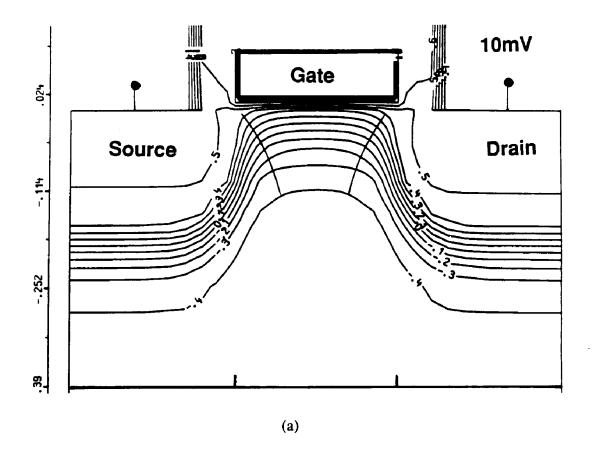

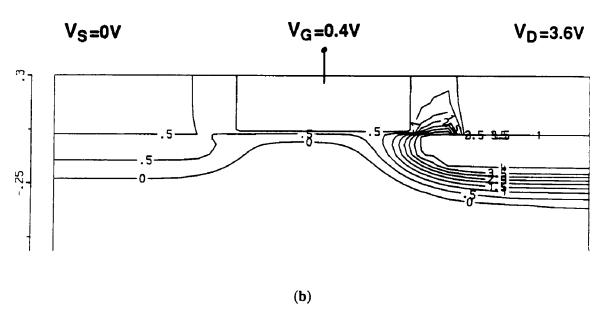

| Figure 2-4.  | Simulated equi-potential contours of a 0.5 $\mu$ m channel length, $V_{GS}$ = 0.3V, and $V_S$ = $V_{SB}$ =0V, (a) $V_{DS}$ =10mV (b) $V_{DS}$ =3.6V.                                                 | 40 |

| Figure 2-5.  | MOS device operates in saturation mode.                                                                                                                                                              | 49 |

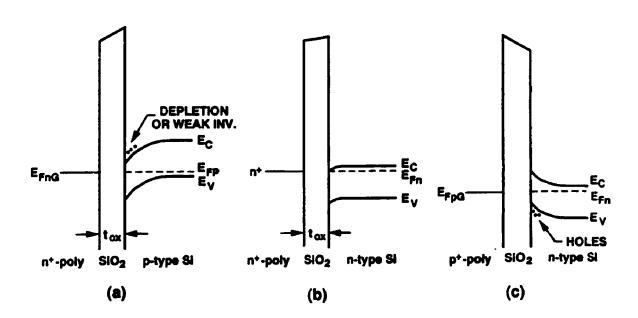

| Figure 3-1.  | Band bending of n+ Polysilicon gate on p- and n-type Si.                                                                                                                                             | 58 |

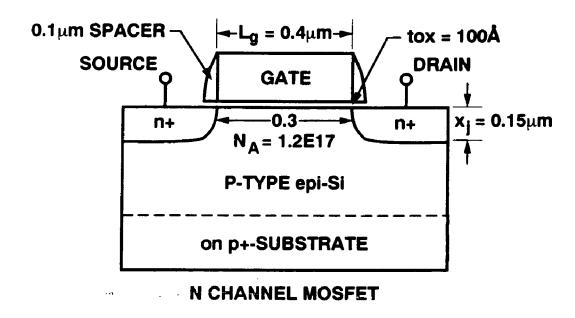

| Figure 3-2.  | Dimensions of a 0.4µm MOS device.                                                                                                                                                                    | 62 |

| Figure 3-3.  | Drain Structures for Hot Carriers Analysis.                                                                                                                                                          | 63 |

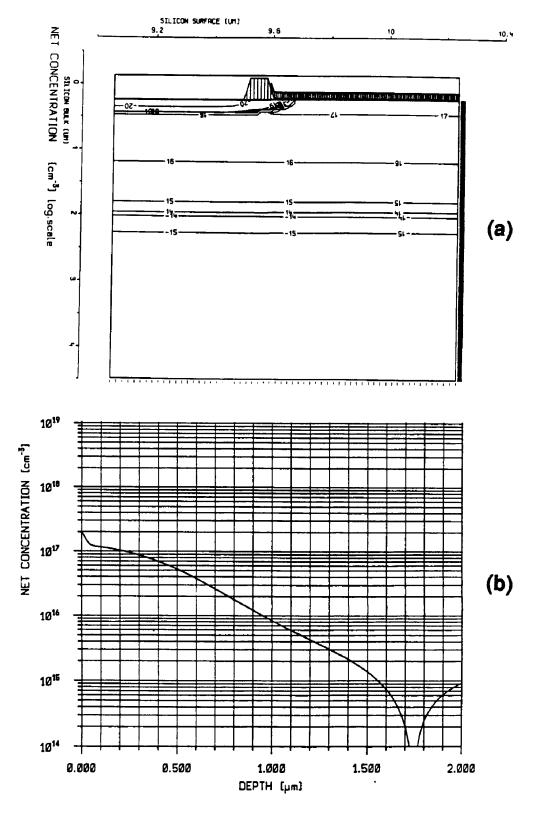

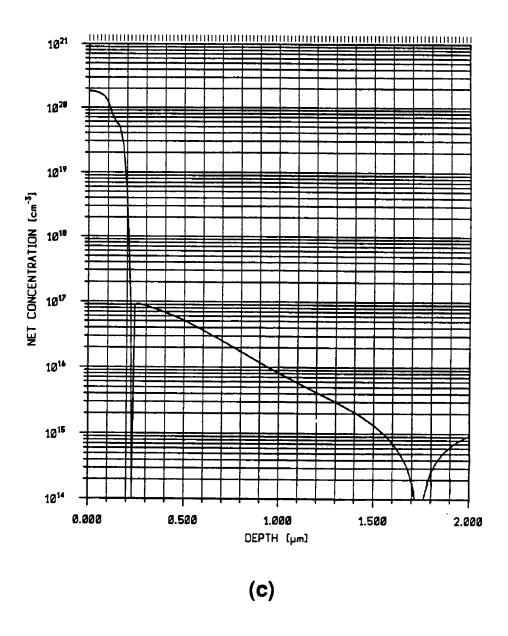

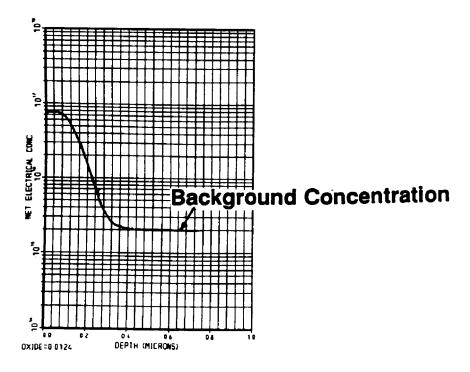

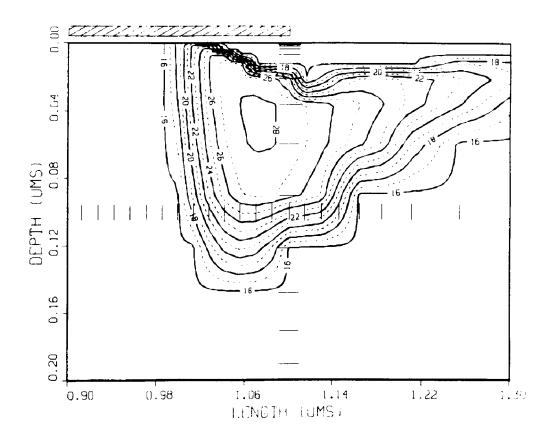

| Figure 3-4.  | NMOS doping profiles: (a) 2-D profile of s/d and channel; (b) 1-D profile in the channel; (c) 1-D s/d junction profile.                                                                              | 69 |

| Figure 3-5.  | PMOS doping profiles: (a) 2-D profile of s/d and channel; (b) 1-D profile in the channel; (c) 1-D s/d junction profile.                                                                              | 71 |

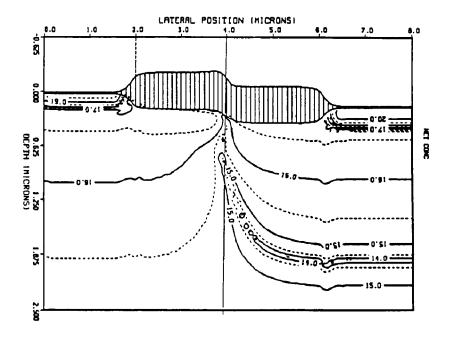

| Figure 3-6.  | 2-D Profile of dopant concentrations at the tub boundary for an advanced twin-tub CMOS using high pressure oxidation for field isolation.                                                            | 72 |

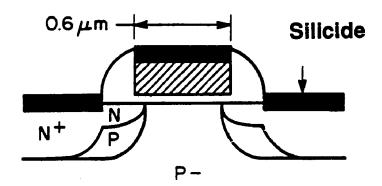

| Figure 3-7.  | Cross-section of a halo-drain NMOS device.                                                                                                                                                           | 76 |

| Figure 3-8.  | 1-D Doping profile in the channel.                                                                                                                                                                   | 77 |

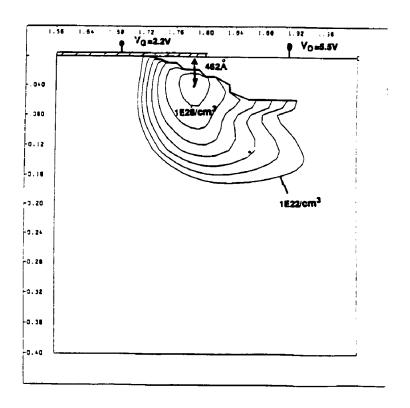

| Figure 3-9.  | Hot carrier generation center in a n-ch halo device.                                                                                                                                                 | 78 |

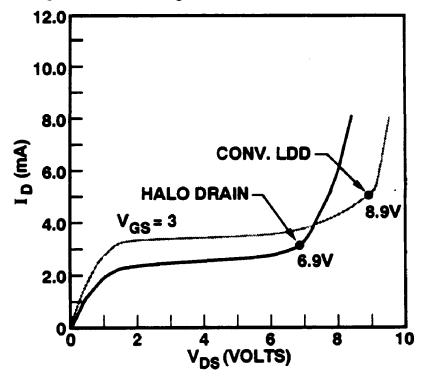

| Figure 3-10. | Measured Source-Drain Breakdown of conventional LDD and Halo-LDD NMOS Devices with effective channel lengths of 0.8 µm.                                                                              | 79 |

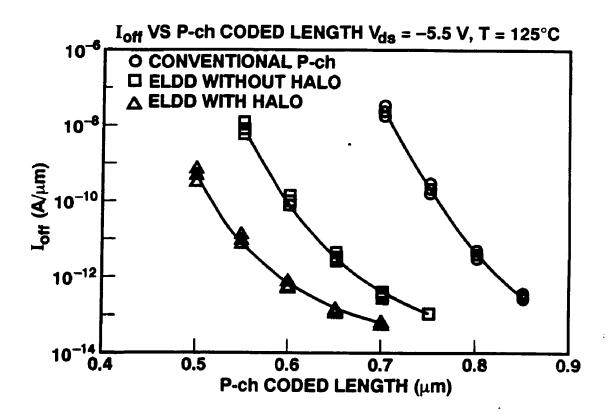

| Figure 3-11. | $I_{off}$ vs $L_{eff}$ of p-ch halo and conventional devices.                                                                                                                                        | 79 |

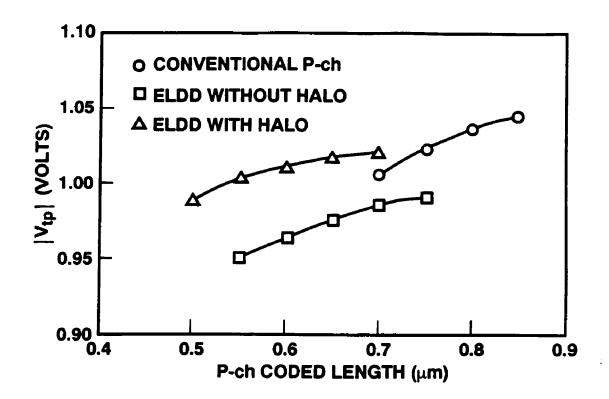

| Figure 3-12. | $V_{tp}$ vs $L_{eff}$ of p-ch halo and conventional devices.                                                                                                                                         | 80 |

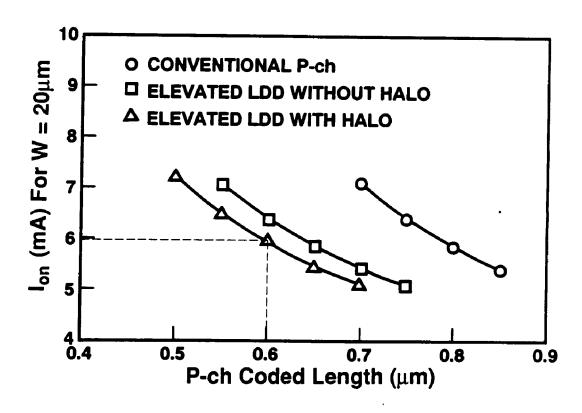

|              | $I_{on}$ vs $L_{eff}$ of p-ch halo and conventional devices.                                                                                                                                         | 81 |

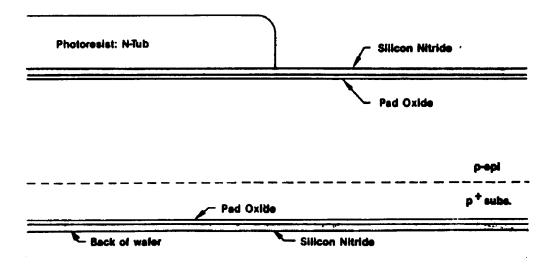

|              | N-tub Photo Resist Step.                                                                                                                                                                             | 82 |

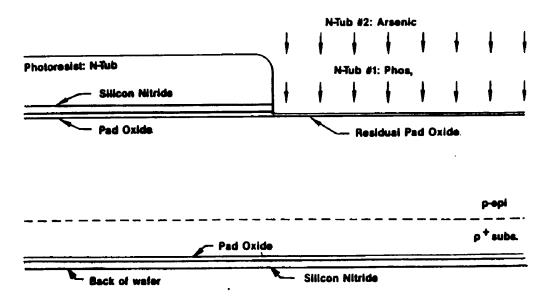

| Figure 4-2.  | N-tub Implant.                                                                                                                                                                                       | 83 |

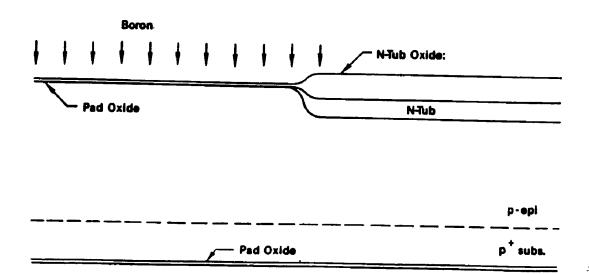

| Figure 4-3   | N-tub Oxidation and self-aligned P-tub implant                                                                                                                                                       | 84 |

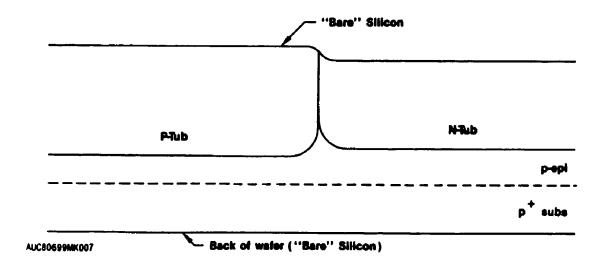

| Figure 4-4.  | Wafer topography after tub formation.                                                                                                                          | 85  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

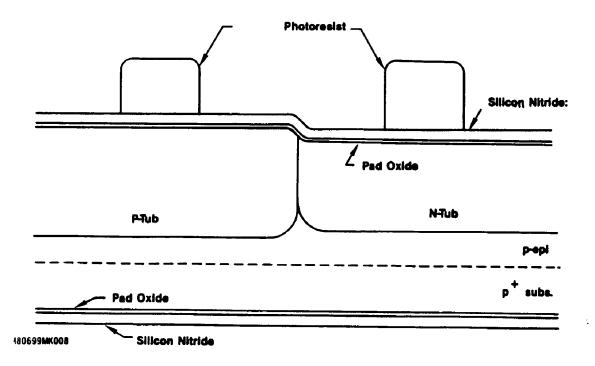

| Figure 4-5.  | Photo Resist Active Area.                                                                                                                                      | 87  |

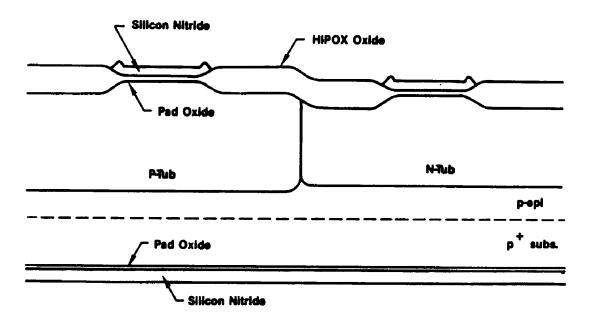

| Figure 4-6.  | Device Cross-Section After Field Oxidation.                                                                                                                    | 88  |

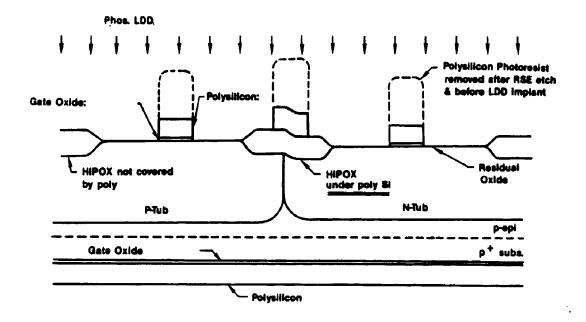

| Figure 4-7.  | Polysilicon Gate Photoresist and Etching.                                                                                                                      | 89  |

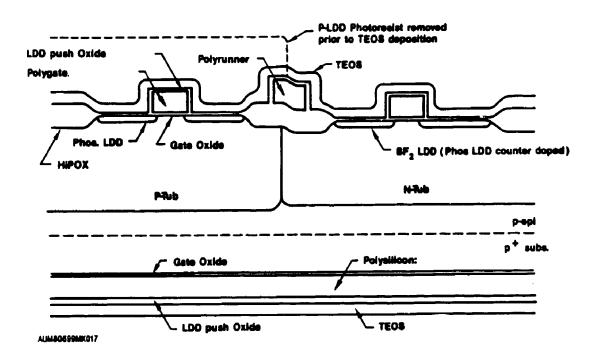

| Figure 4-8.  | Sidewall Spacer Formation.                                                                                                                                     | 90  |

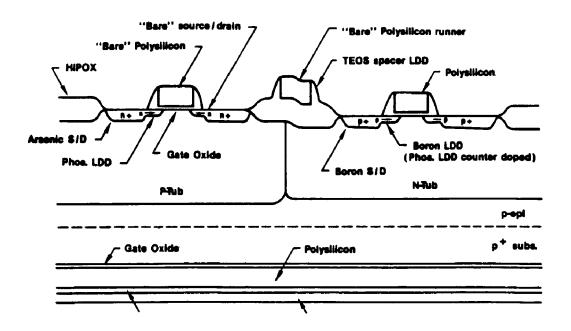

| Figure 4-9.  | Device Structure Before Ti Deposition.                                                                                                                         | 91  |

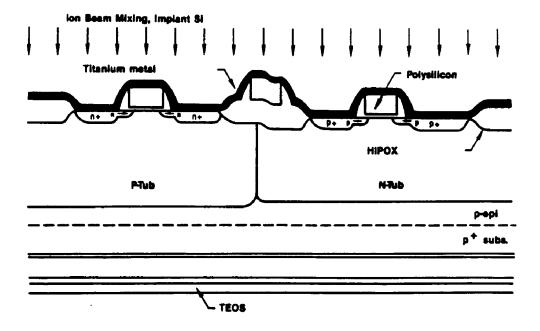

| Figure 4-10. | Ti Deposition and Ion Mixing Implant.                                                                                                                          | 92  |

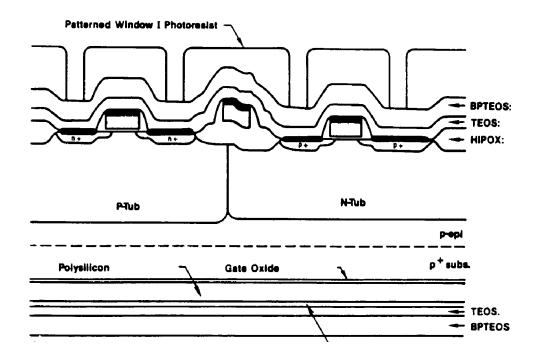

| Figure 4-11. | Selective Silicide Reaction, Dielectric 1 and Window 1 PR.                                                                                                     | 93  |

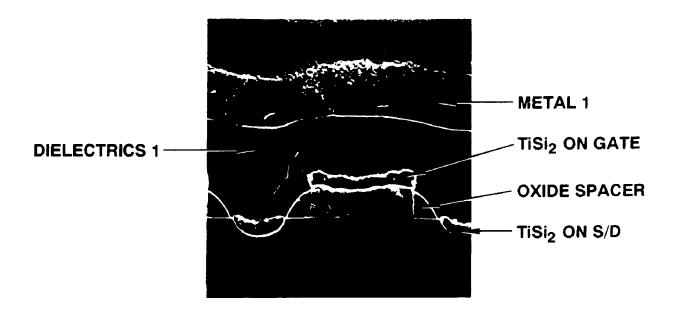

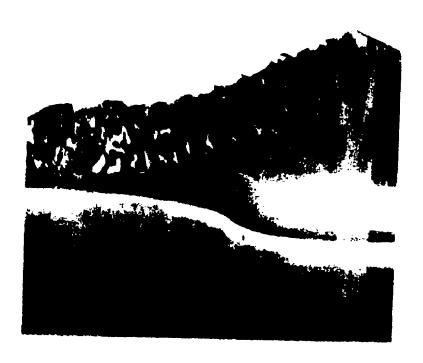

| Figure 4-12. | SEM micrograph of a finished MOS device with Ti silicide and first level metal dielectric.                                                                     | 94  |

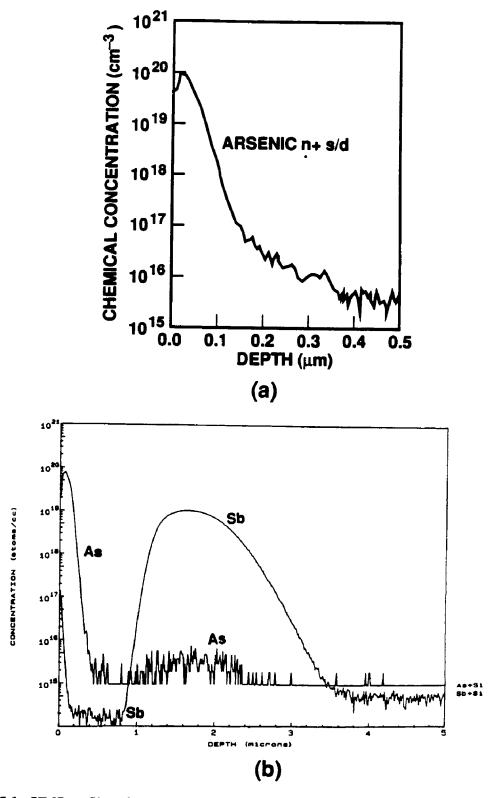

| Figure 5-1.  | SIMS profiles of an n+ source/drain junction (a), and an npn buried layer and emitter (b)(SIMS work done by F. Stevie at AT&T Bell Labs).                      | 99  |

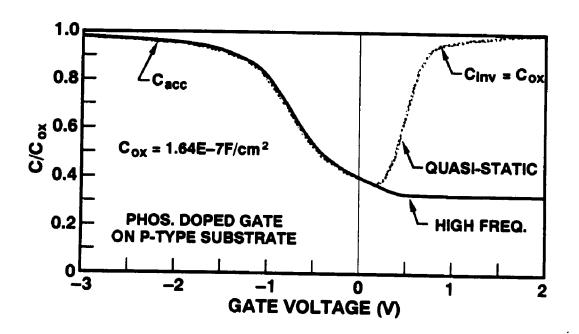

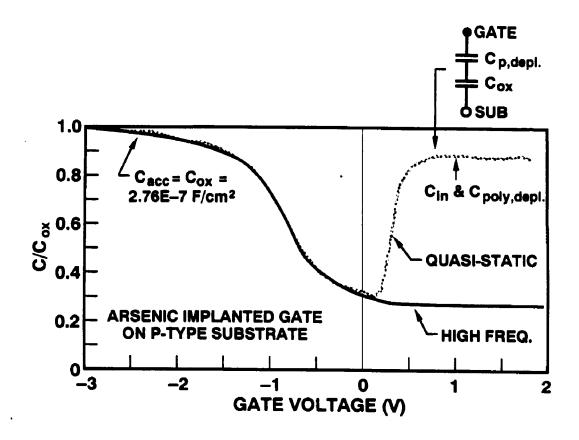

| Figure 5-2.  | High frequency and quasi-static C-V curves of an MOS capacitors with a phosphorus diffused gate, with an area of $0.56\text{E}-3cm^2$ , $t_{ox}=208\text{A}$ . | 102 |

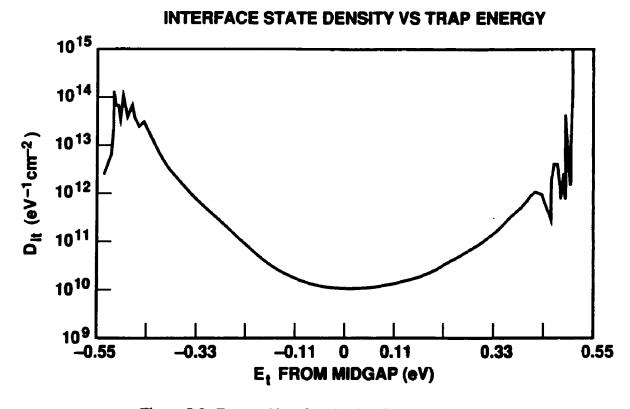

| Figure 5-3.  | Extracted interface density, $D_{it}$ , vs energy.                                                                                                             | 102 |

| Figure 5-4.  | Quasi-Static C-V curves an arsenic implanted, not fully activated poly gate capacitor.                                                                         | 103 |

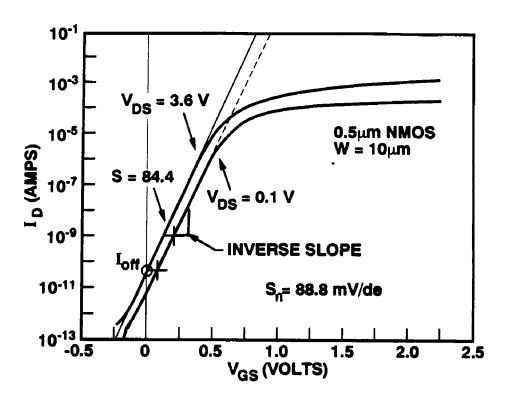

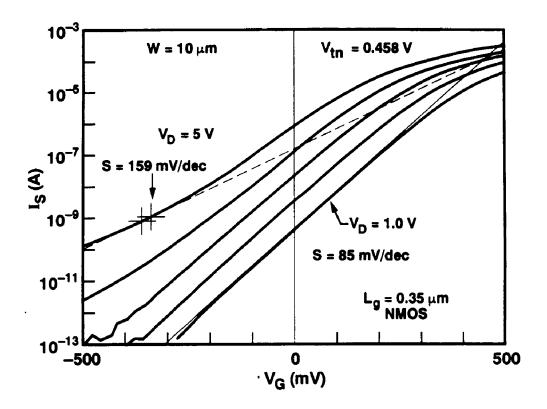

| Figure 5-5.  | $Log(I_D)$ vs $V_G$ curves of an NMOSFET with $L_{eff}$ =0.45 $\mu$ m and at 2 different drain bias.                                                           | 106 |

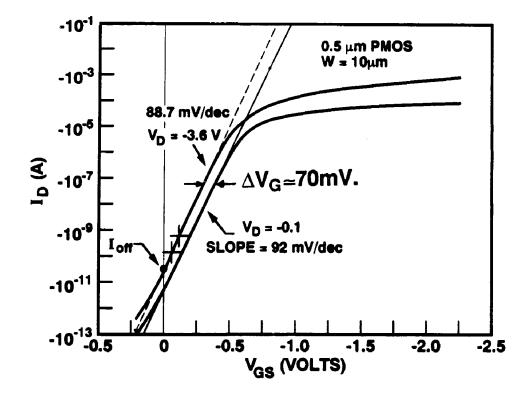

| Figure 5-6.  | $Log(I_D)$ vs $V_G$ curves of a PMOSFET with $L_{eff}$ =0.43 $\mu$ m and at 2 different drain bias.                                                            | 107 |

| Figure 5-7.  | Subthreshold g-curves of a $0.3\mu m$ channel length NMOSFET operates near punch-through.                                                                      | 107 |

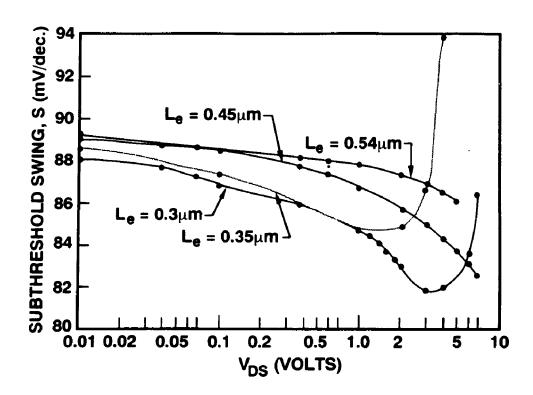

| Figure 5-8.  | Reverse $SubV_t$ Swing vs Drain Bias for sub-half micron NMOS devices.                                                                                         | 109 |

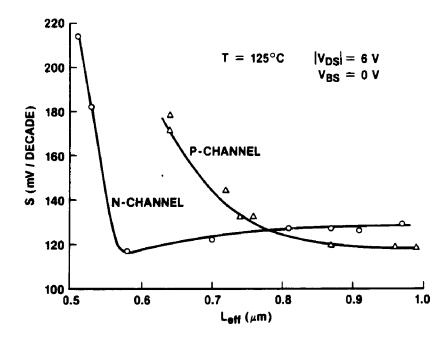

| Figure 5-9.  | Reverse SubV <sub>t</sub> Swing on NMOS with respect to channel length, while PMOS buried channel devices shows monotonically increasing S. <sup>[50]</sup>    | 109 |

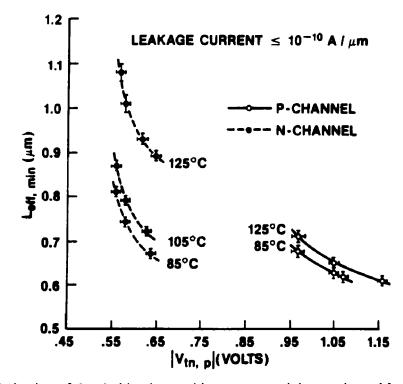

| Figure 5-10. | $I_{off}$ vs $L_{eff}$ for N and PMOS devices at 125°C and at different $V_{tn}$ 's and $V_{tp}$ 's.                                                           | 111 |

| Figure 5-11. | Optimization of threshold voltage with respect to minimum channel length and $I_{\it off}$ requirements at different temperatures.                             | 111 |

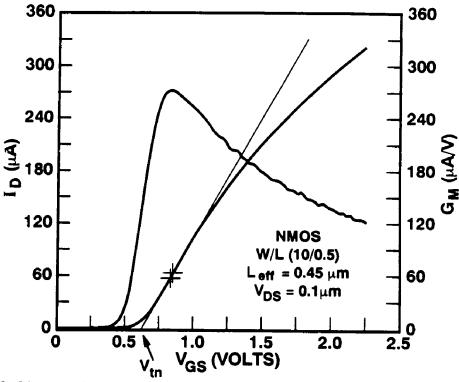

| Figure 5-12. | Linear drain current and its transconductance as a function of gate voltage for a 0.45 $\mu m$ NMOS device.                                                    | 113 |

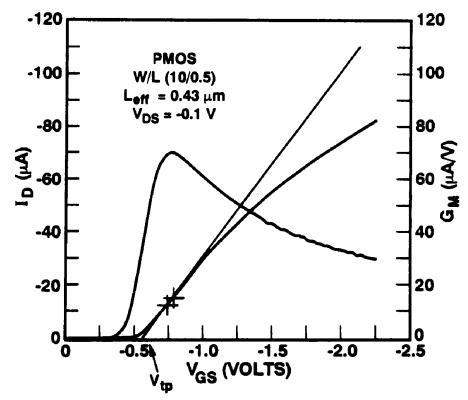

| Figure 5-13. | Linear drain current and its transconductance as a function of gate voltage for a 0.43µm PMOS device.                                                          | 113 |

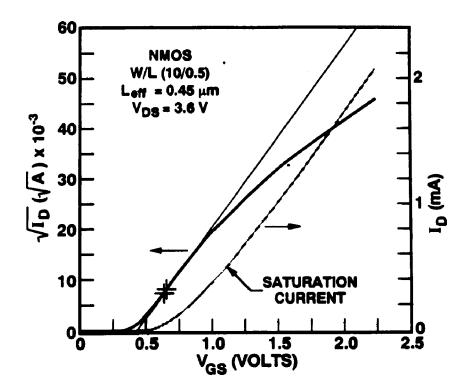

| Figure 5-14. | Plot of $I_D$ and $\sqrt{I_D}$ for an NMOS device, with the drain biased at $V_D$ =3.6V.                                                                       | 114 |

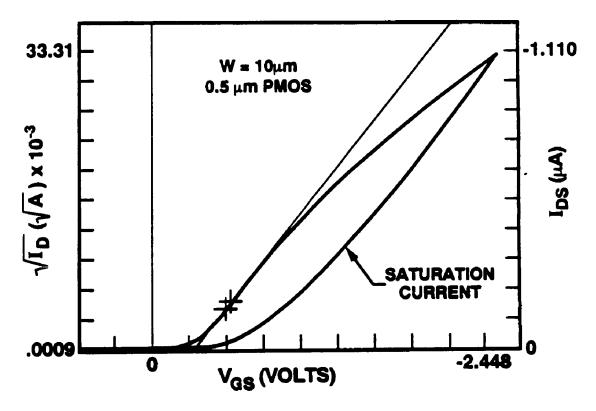

| Figure 5-15. | Plot of $I_D$ and $\sqrt{I_D}$ for an PMOS device, with the drain biased at $V_D = -3.6$ V.                                                                    | 115 |

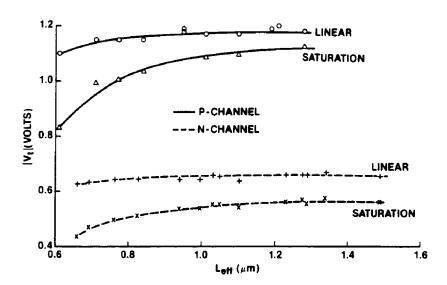

| Figure 5-16. | Linear and saturation threshold voltage vs. $L_{eff}$ for n and p-channel transistors. <sup>[50]</sup>                                                         | 115 |

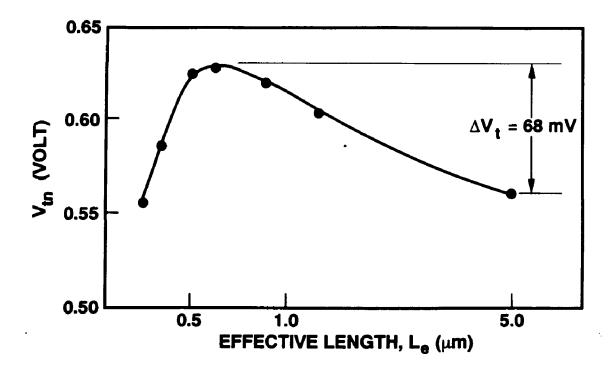

|              | Reverse short channel effect in NMOS Devices with lower surface concentration.                                                                                 | 116 |

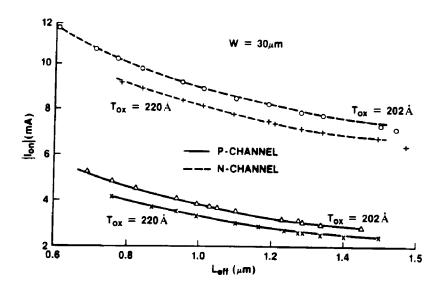

| Figure 5-18. | $I_{on}$ vs $L_{eff}$ of n- and buried p-ch MOSFETs.                                                                                                           | 118 |

|              |                                                                                                                                                                |     |

| Figure 5-19. | Change in threshold voltage vs $\sqrt{V_{SB} + 2\phi_F} - \sqrt{2\phi_F}$ .                                                                                            | 120 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5-20. | Shift in threshold voltage for conventional as a function of back gate voltages.                                                                                       | 121 |

| Figure 5-21. | Shift in threshold voltage for halo drain device with $V_{in}(0)=0.8$ V, as a function of back gate voltages.                                                          | 122 |

| Figure 5-22. | Source Voltage of a source follower transistor (or transfer gate), shows the different in $V_s$ for the conventional and halo-drain device.                            | 122 |

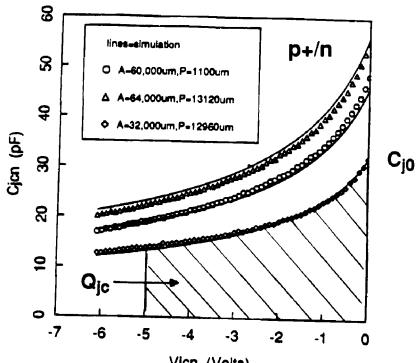

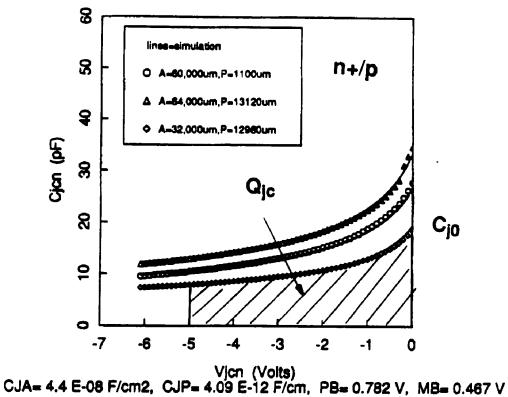

| Figure 5-23. | Junction Capacitances of 3 n+/p diodes with different areas and perimeters.                                                                                            | 124 |

| Figure 5-24. | Junction Capacitances of 3 p+/n diodes with different areas and perimeters.                                                                                            | 125 |

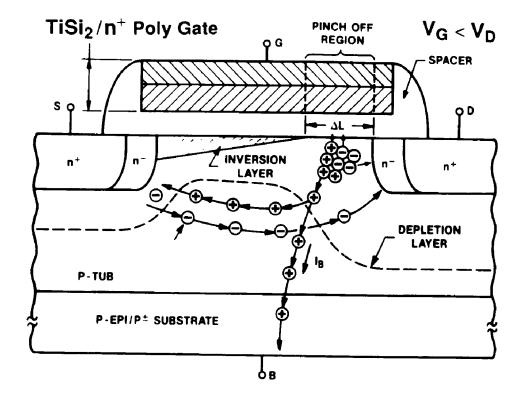

| Figure 6-1.  | The processes of hot carrier generation, injection and drain-source breakdown conditions.                                                                              | 129 |

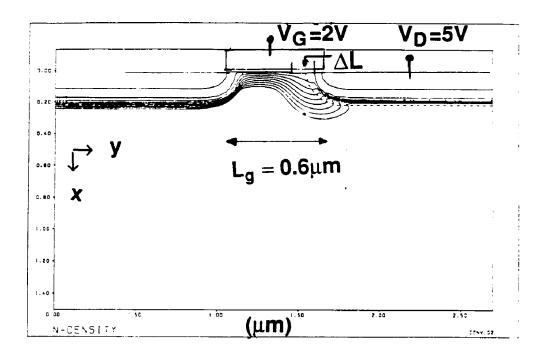

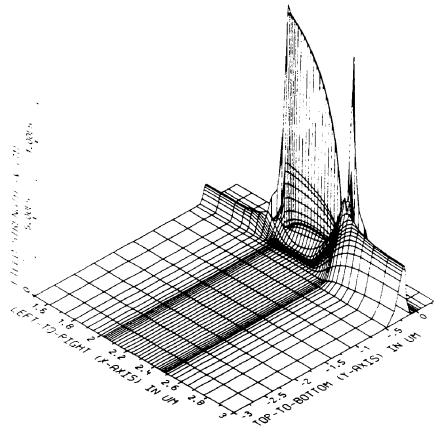

| Figure 6-2.  | 3-D channel electric field for a DDD drain structure with $V_D$ =5V and $V_G$ =2V, $E_m$ is calculated to be 2E6V/cm.                                                  | 130 |

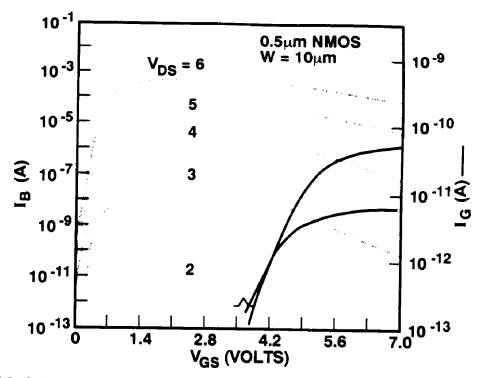

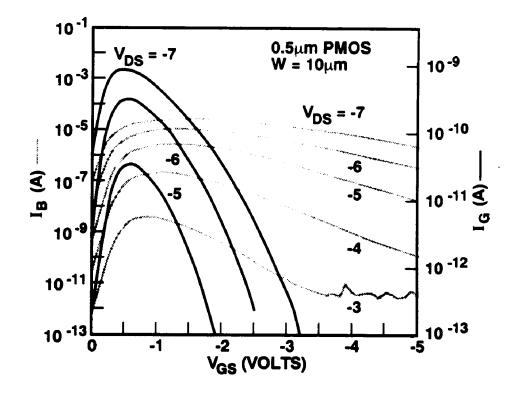

| Figure 6-3.  | Substrate current and gate currents as a function of $V_{GS}$ at different $V_{DS}$ 's for a 0.45 $\mu m$ NMOSFET.                                                     | 132 |

| Figure 6-4.  | Substrate current and gate currents as a function of $V_{GS}$ at different $V_{DS}$ 's for a 0.43 $\mu m$ PMOSFET.                                                     | 132 |

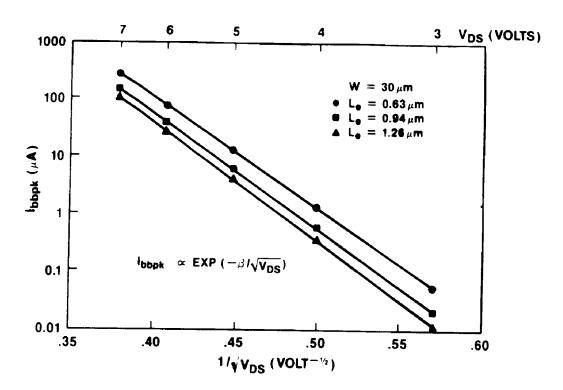

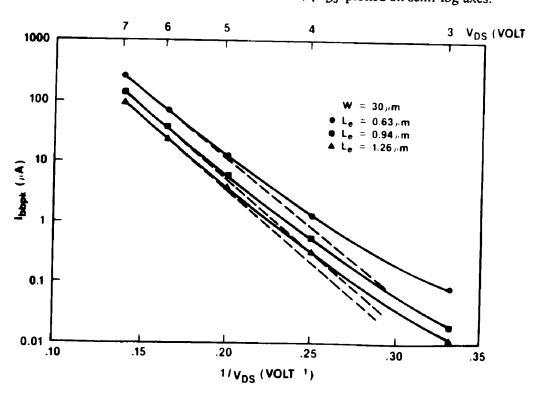

| Figure 6-5.  | The maximum substrate current vs $1/\sqrt{V_{DS}}$ plotted on semi-log axes.                                                                                           | 134 |

| Figure 6-6.  | A conventional plot of $I_{B,max}$ vs $1/V_{DS}$ [101], indicating a deviation from the straight lines at low $V_{DS}$ 's.                                             | 134 |

| Figure 6-7.  | Generation center of Hot Carriers and Hot Electron Injected Gate Current.                                                                                              | 136 |

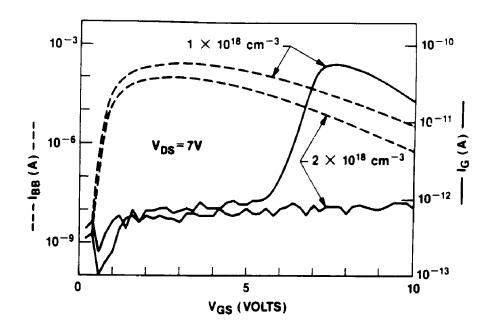

| Figure 6-8.  | Substrate and gate current for the .98µm NMOS transistors with spacer width of 0.24µm and 2 different n- implants. [50]                                                | 140 |

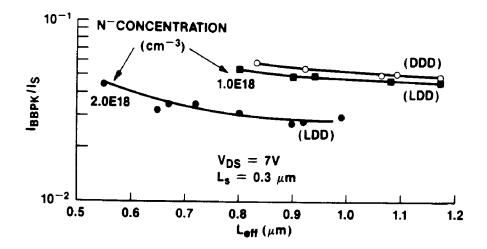

| Figure 6-9.  | Normalized peak substrate current $(I_{sub,max}/I_S)$ vs $L_{eff}$ for LDD and DDD n-ch devices. [50]                                                                  | 141 |

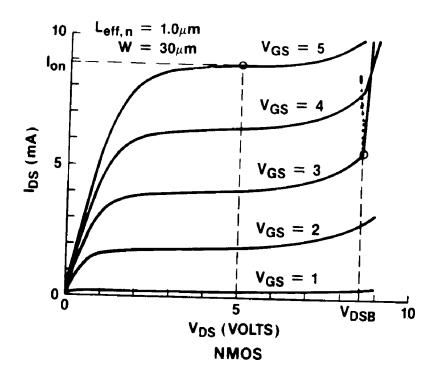

| Figure 6-10. | A typical $I_{DS}$ vs $V_{DS}$ illustrates the measured breakdown voltage, $V_{DSB}$ .                                                                                 | 142 |

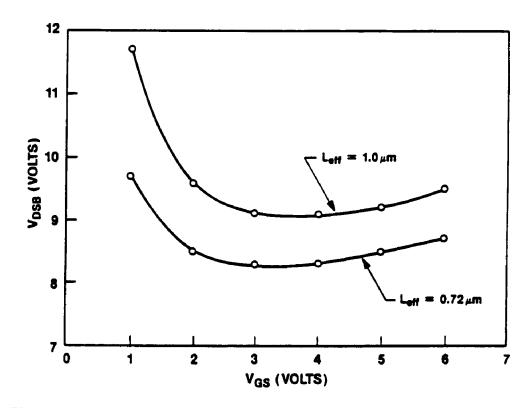

| Figure 6-11. | Breakdown voltage as a function of gate voltage for an NMOS device.                                                                                                    | 143 |

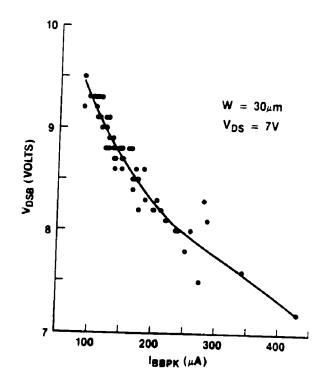

| Figure 6-14. | Correlation between drain-source breakdown voltage and peak substrate current, $I_{B,max}$ . Substrate current measured at $V_{DS} = 7$ V. Channel lengths are varied. | 143 |

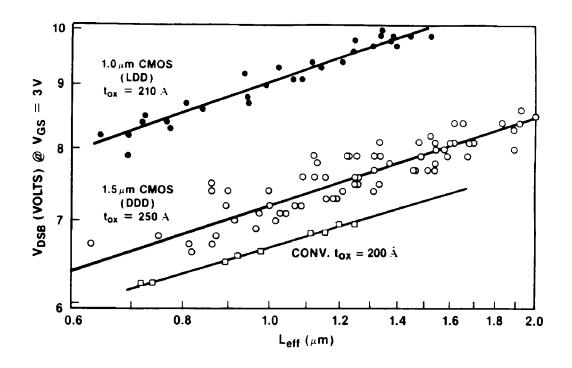

| Figure 6-12. | $V_{DSB}$ at $V_G$ =3V as a function of effective channel length for different NMOS device structures, 1.0 $\mu$ m (LDD); 1.5 $\mu$ m (DDD) devices.                   | 144 |

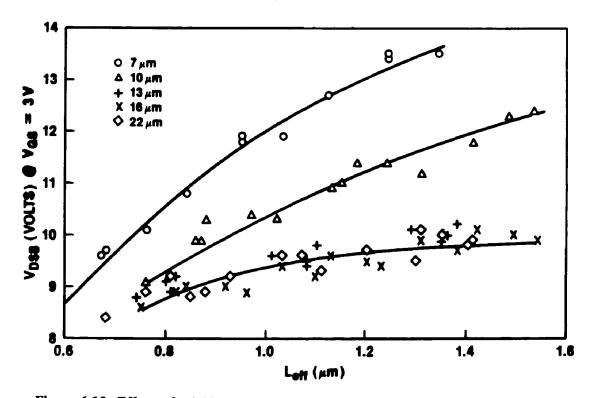

| Figure 6-13. | Effects of epi thickness (effective bulk resistance) on breakdown voltages.                                                                                            | 144 |

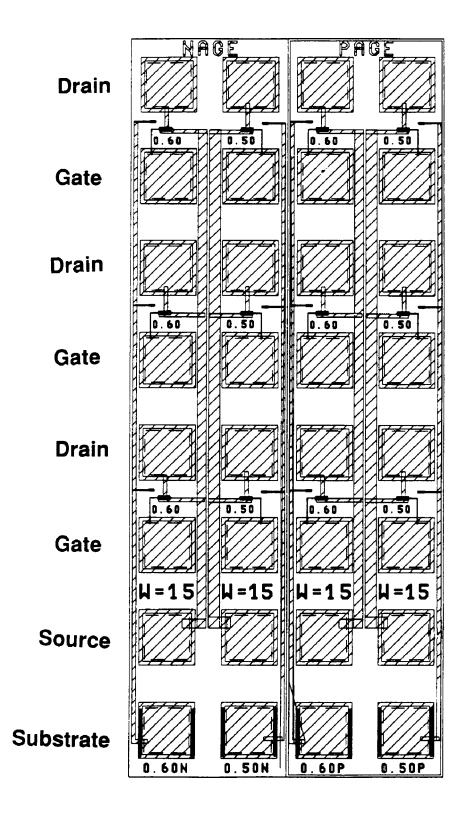

| Figure 7-1.  | Layout of 0.5 and 0.6µm CMOS devices for DC aging experiments.                                                                                                         | 147 |

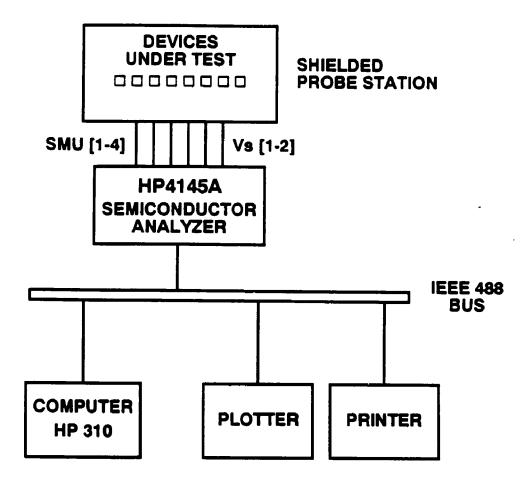

| Figure 7-2.  | Aging Stress Measurement System with a shielded probe station.                                                                                                         | 148 |

| Figure 7-3.  | Typical transfer characteristics in linear mode before and after dc bias stress. <sup>[100]</sup>                                                                      | 149 |

| Figure 7-4.  | Subthreshold curves in linear and saturation mode to monitor subthreshold swing S and $I_{crit}$ [100]                                                                 | 150 |

| Figure 7-5.  | Changes in transconductance, $g_m$ , and threshold voltage, $V_{ln}$ , vs stress time.                                                                           | 151 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7-6.  | Forward (dashed) and reverse (dotted curves) $I_D$ - $V_D$ characteristics before and after stress.                                                              | 152 |

| Figure 7-7.  | Channel and substrate currents after stress in forward and reverse modes indicate an increase in breakdown voltage in reverse mode.                              | 153 |

| Figure 7-8.  | Substrate currents before stress (solid curves) and after stress in forward and reverse modes.                                                                   | 154 |

| Figure 7-9.  | Drain junction leakage after 170 minutes stress on a 0.61 µm transistor. Dotted lines show reverse mode channel current measured at the source.                  | 154 |

| Figure 7-10. | $I_D$ vs $V_G$ transfer curve and its first and second derivatives.                                                                                              | 158 |

|              | Normalized $R_{mn}$ and $I_{DS}$ plots vs $V_{DS}$ for $m/n$ evaluation.                                                                                         | 159 |

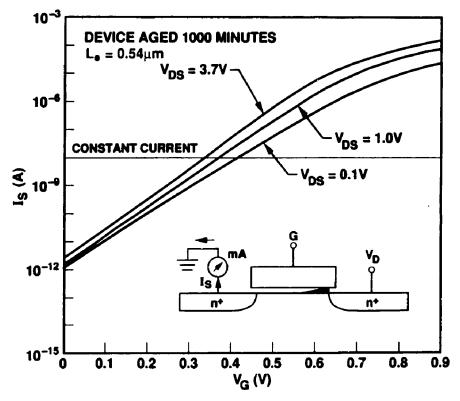

|              | Subthreshold $g$ curves before and after 1000 mins. stress for a 0.54 $\mu$ m NMOS devices. The parameter $n$ is extracted at a constant drain current of 10nA.  | 160 |

| Figure 7-13. | The $g$ curves of an aged device at different drain bias, $n$ is extracted at constant channel (source) current of $10nA$ .                                      | 161 |

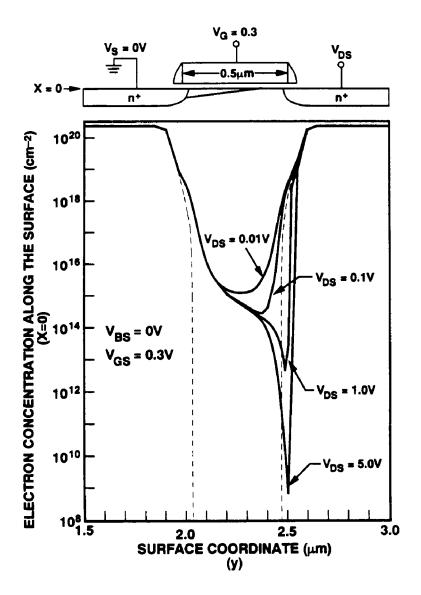

| Figure 7-14. | Surface electron density showing a depletion of electrons at the drain when the drain bias is increased.                                                         | 163 |

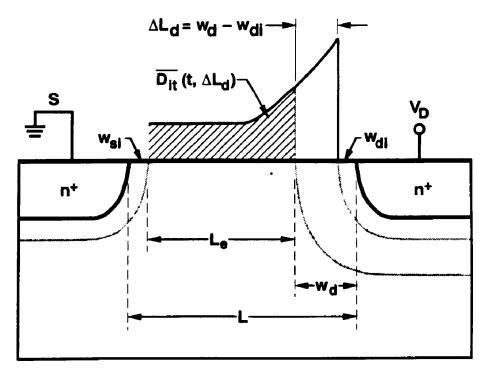

| Figure 7-15. | Schematic illustrates the distribution of interface states along the channel length.                                                                             | 164 |

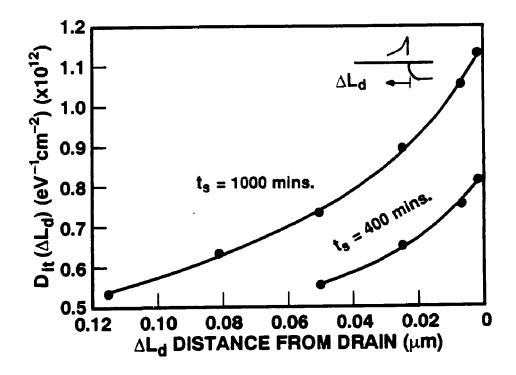

| Figure 7-16. | Experimental spatial distribution of interface state density at the drain of an NMOSFET with $L_{eff} = 0.54  \mu \text{m}$ aged at 5.5V, for 400 and 1000 mins. | 164 |

| Figure 7-17. | Interface trap built-up with time at the 2 edges of $\Delta L_d$ .                                                                                               | 167 |

| Figure 7-18. | $\overline{D_{ii}}$ built-up along the drain at various stress times.                                                                                            | 168 |

| Figure 7-19. | Two-Transistor Model with non-uniformed defect region.                                                                                                           | 168 |

| Figure 7-20. | Subthreshold $g$ curves for an aged device measured in the reverse-mode, the sub $V_t$ swings do not change as the reversed source voltage varies.               | 169 |

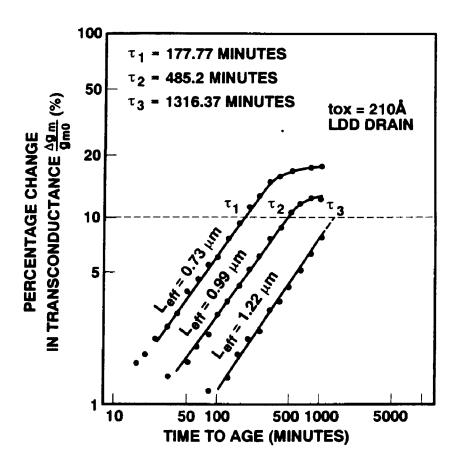

| Figure 7-21. | $g_m$ degradation for 3 LDD NMOS devices with different channel lengths, $t_{ox}$ =210Å.                                                                         | 170 |

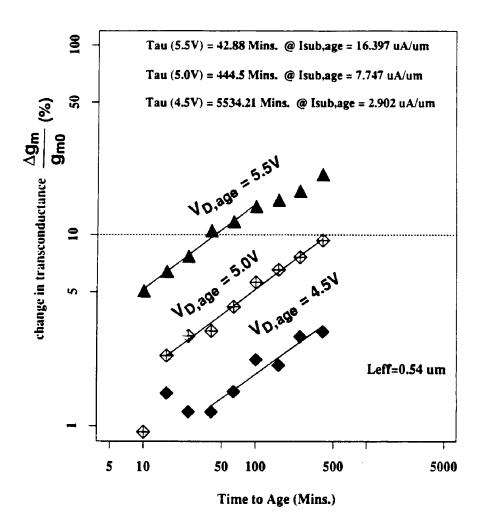

| Figure 7-22. | Typical $g_m$ degradation curves for 3 devices with the same effective lengths of $L_e$ =0.54 $\mu$ m.                                                           | 173 |

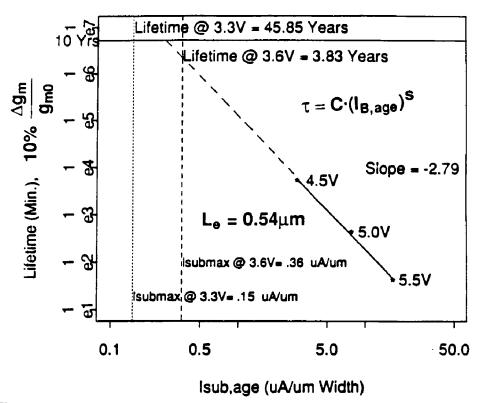

| Figure 7-23. | Lifetime vs substrate current during aging for the devices shown in Fig7-22.                                                                                     | 174 |

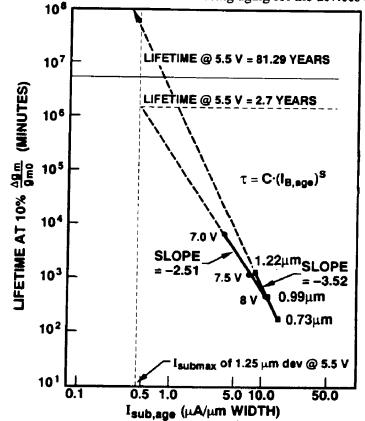

| Figure 7-24. | Lifetime extrapolation of devices aged with different channel lengths and voltages.                                                                              | 175 |

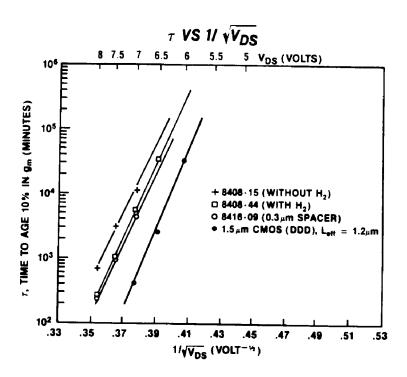

| Figure 7-25. | A more accurate plot of lifetime vs $1/\sqrt{V_{DS}}$ , to extrapolate to 5 V and below.                                                                         | 176 |

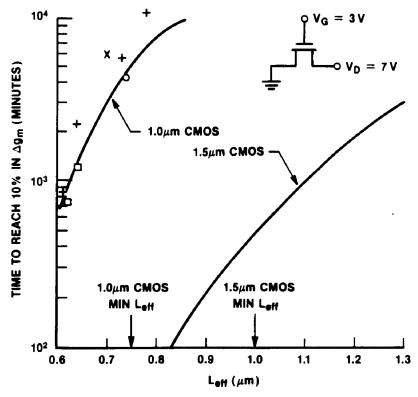

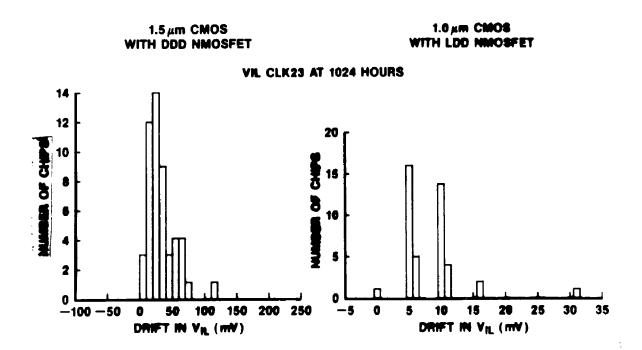

| Figure 7-26. | Lifetime vs $L_{eff}$ for the 1.0µm CMOS devices, using NLDD with $t_{ox}$ =210Å and 1.5µm NMOS with DDD drain and $t_{ox}$ =250Å. [50]                          | 177 |

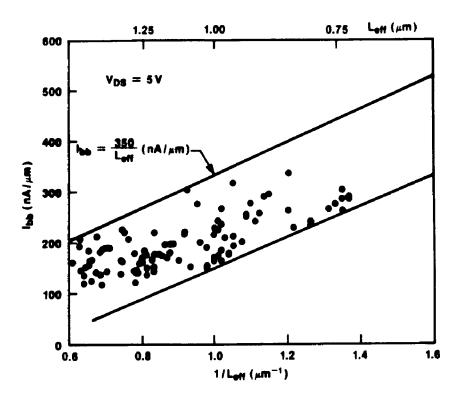

| Figure 7-27. | Maximum substrate current as a function of $1/L_{\it eff}$ for devices with $L_{\it eff}$ from 0.75 $\mu$ m to 1.3 $\mu$ m.                                      | 178 |

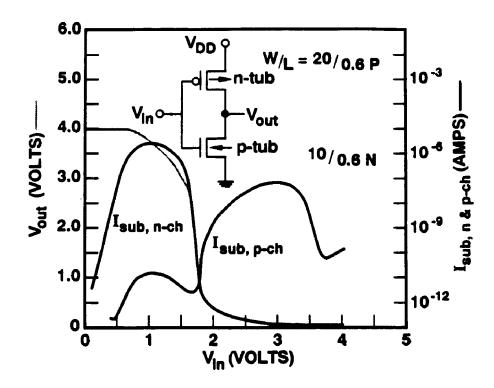

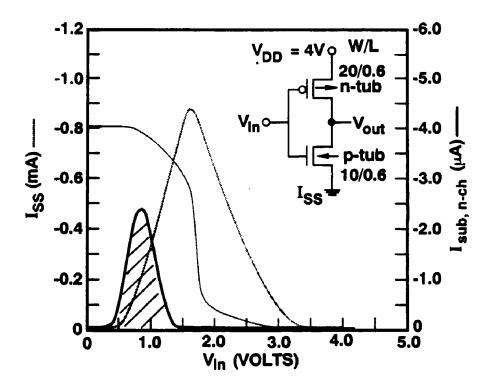

| Figure 7-28. | n & p-ch substrate (bulk) currents during switching of a CMOS inverter.                                                                                          | 179 |

| Figure 7-29. | Averaged substrate current during inverter switching.                                                                                                                              | 180 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7-30. | Circuit drift from hot carrier stressing. (The circuit aging was performed by P. Kempsey).                                                                                         | 181 |

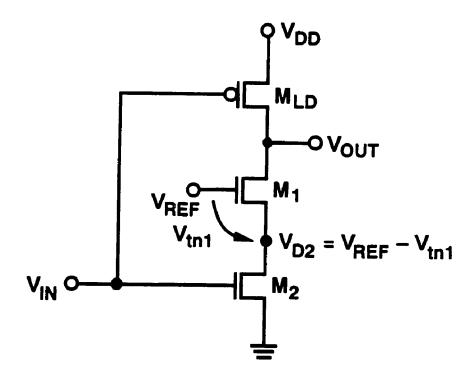

| Figure 7-31. | Series transistors connected in a cascode configuration to reduce hot carrier aging.                                                                                               | 181 |

| Figure 8-1.  | Conventional LOCOS Isolation.                                                                                                                                                      | 184 |

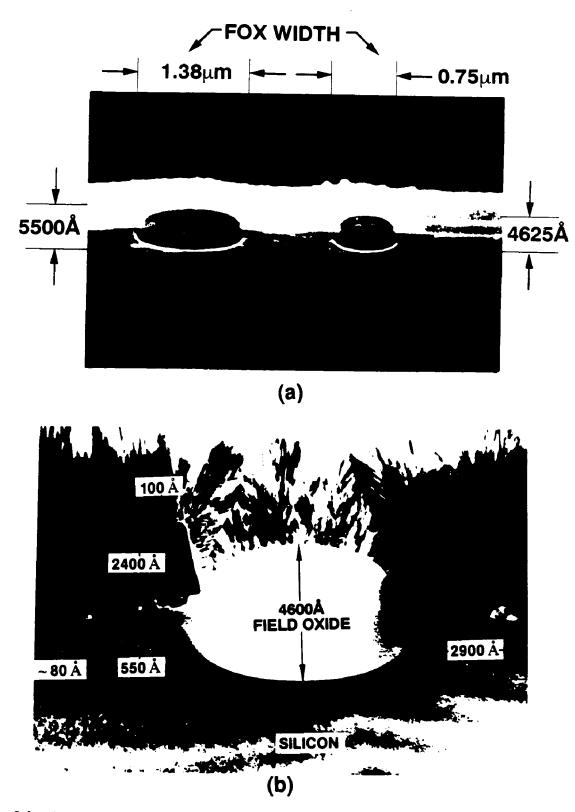

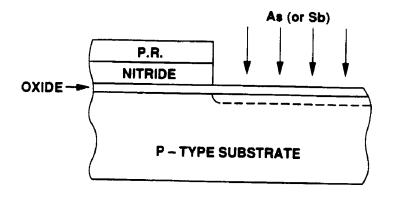

| Figure 8-2.  | Field oxide thinning in narrow space, (a) for .75µm spacing, oxide is thinned by 875A compared with 1.38µm space. (b) TEM cross section shows the stress region on the poly layer. | 185 |

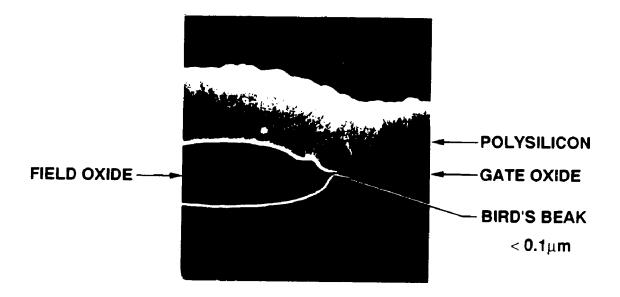

| Figure 8-3.  | The final Bird's Beak at the edge of field oxide and gate oxide.                                                                                                                   | 187 |

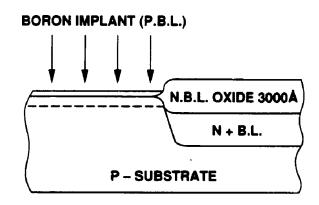

| Figure 8-4.  | Buried layer protection oxide and the self-aligned p isolation implant.                                                                                                            | 190 |

| Figure 8-5.  | Deep-collector implant.                                                                                                                                                            | 190 |

| Figure 8-6.  | Reverse Emitter Window process to form emitter and collector implant.                                                                                                              | 192 |

| Figure 8-7.  | Emitter window and base and optional local intrinsic collector implants.                                                                                                           | 194 |

| Figure 8-8.  | Doping Profile of Emitter-Base-Collector with a local collector implant.                                                                                                           | 195 |

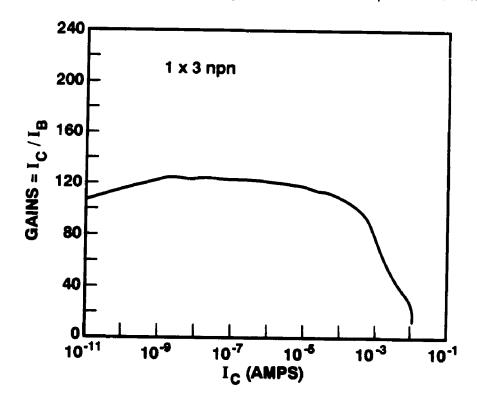

| Figure 8-9.  | Gummel Plot of an npn bipolar transistor with $1\times3 \mu m^2$ Emitter window.                                                                                                   | 196 |

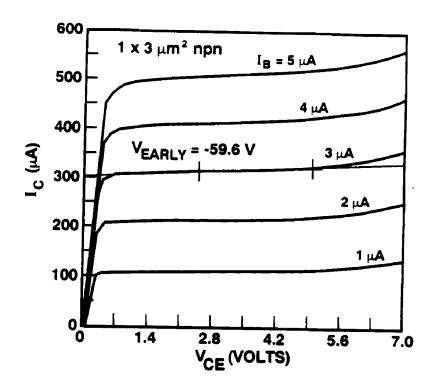

| Figure 8-10. | Bipolar gain vs collector current.                                                                                                                                                 | 197 |

| Figure 8-11. | $I_C$ vs $V_{CE}$ characteristics.                                                                                                                                                 | 197 |

#### LIST OF TABLES

| TABLE 1-1. Conventional Scaling Law                                                                | 19  |

|----------------------------------------------------------------------------------------------------|-----|

| TABLE 1-2. Practical Scaling of CMOS Devices                                                       | 20  |

| TABLE 5-1. Typical resistance values for different types of material.                              | 104 |

| TABLE 7-1. Changes in Subthreshold Swing vs. Back Gate Bias.                                       | 161 |

| TABLE 7-2. Interface State Density as a function of distance $\Delta L_d$ from the drain junction. | 162 |

## List of Symbols

| Symbols           | Description                                      | Unit               |

|-------------------|--------------------------------------------------|--------------------|

|                   |                                                  |                    |

| Α                 | device Area                                      | cm <sup>2</sup>    |

| α                 | depletion width coefficient                      | $cmV^{-1/2}$       |

| $\alpha_{it}$     | emperical surface reduction factor               | cm <sup>2</sup>    |

| $\beta_o$         | MOS Transistor gain                              | A $V^{-2}$         |

| $C_{ox}$          | gate oxide capacitance (per unit area)           | $F/cm^2$           |

| $C_{it}$          | interface trap capacitance                       | $F/cm^2$           |

| $C_n$             | n-ch inversion layer capacitance                 | $F/cm^2$           |

| $C_{p}$           | p-ch inversion layer capacitance                 | $F/cm^2$           |

| $C_{\mathcal{D}}$ | depletion layer capacitance                      | $F/cm^2$           |

| $C_s$             | semiconductor layer capacitance                  | $F/cm^2$           |

| $C_G$             | MOS gate capacitance                             | $F/cm^2$           |

| δ                 | drain effect term on threshold voltage           |                    |

| $D_{it}$          | interface state density                          | $eV^{-1}cm^{-2}$   |

| $\Delta g_m$      | change in transconductance g <sub>m</sub>        | S                  |

| $\delta L$        | total change in $L_m$ due to lateral             |                    |

|                   | diffusion and gate etching                       | cm                 |

| $\Delta L$        | pinch-off length in saturation                   | cm                 |

| $\Delta L_d$      | damaged length from the drain due to hot carrier | cm                 |

| $\Delta V_t$      | change in threshold voltage $V_t$                | V                  |

| $\epsilon_o$      | vacuum dielectric constant                       | 8.85E-14 F/cm      |

| $\epsilon_{ox}$   | oxide dielectric constant                        | 3.9€₀              |

| $\epsilon_s$      | silicon dielectric constant                      | 11.8ε <sub>ο</sub> |

| $E_c$             | silicon conduction band-edge energy              | eV                 |

| $E_t$             | interface trap energy in the bandgap             | eV                 |

| $E_{\nu}$         | silicon valence band-edge energy                 | eV                 |

| $E_i$             | silicon intrinsic Fermi level in the bulk        | eV                 |

| $E_{is}$          | silicon intrinsic Fermi level at the surface     | eV                 |

| $E_{Fn}$          | Fermi level of electrons                         | eV                 |

| $E_{Fp}$          | Fermi level of holes                                         | eV                      |

|-------------------|--------------------------------------------------------------|-------------------------|

| $f_t$             | interface trap occupancy function                            |                         |

| γ                 | band bending over $2\phi_F$                                  | V                       |

| 8m                | MOS transistor transconductance                              | S                       |

| 8mo               | initial transconductance                                     | S                       |

| $I_B$ , $I_{sub}$ | bulk or substrate current                                    | Α                       |

| $I_D, I_{DS}$     | drain current                                                | Α                       |

| $I_G$             | gate current                                                 | Α                       |

| $I_S$             | source current                                               | Α                       |

| $I_{off}$         | drain current at $V_{GS}=0$ and $V_{DS}=\max$ op. voltage    | Α                       |

| $I_{on}$          | drain current at $V_{GS} = V_{DS} = \text{max. op. voltage}$ | Α                       |

| λ                 | body effect coefficient                                      | $V^{-1}$                |

| L                 | channel length between s/d metallurgical junctions           | cm                      |

| $\kappa_{ox}$     | relative dielectric constant of oxide                        | 3.9                     |

| K <sub>s</sub>    | relative dielectric constant of silicon                      | 11.8                    |

| $L_e$ , $L_{eff}$ | electrical or effective channel length                       | cm                      |

| $L_{g}$           | gate electrode length                                        | cm                      |

| $L_m$             | coded (designed mask) gate length                            | cm                      |

| m                 | normalized depletion capacitance to $C_{ox}$                 |                         |

| n                 | normalized total capacitance to oxide capacitance            |                         |

| n'                | exponent of $D_{ii}$ vs stress time                          |                         |

| $n_c$             | density of electrons in the conduction band                  | $cm^{-3}$               |

| $n_i$             | intrinsic electron concentration                             | $cm^{-3}$               |

| $n_s$             | electron surface concentration                               | $cm^{-3}$               |

| $N_A$             | acceptor doping density (p-type)                             | $cm^{-3}$               |

| $N_D$             | donnor doping density (n-type)                               | $cm^{-3}$               |

| $N_{ch}$          | channel doping density                                       | <i>cm</i> <sup>−3</sup> |

| $N_B$             | bulk concentration, (acceptor or donor)                      | $cm^{-3}$               |

| ф                 | quasi Fermi level                                            | V                       |

| $\phi_{Fn}$       | Fermi potential from midgap to $E_{Fn}$                      | V                       |

| $\phi_{Fp}$       | Fermi potential from midgap to $E_{Fp}$                      | V                       |

| $\phi_n$          | quasi Fermi level for electrons                              | V                       |

| $\phi_p$          | quasi Fermi level for holes                                  | v                       |

| φ,                | surface potential, referenced to the bulk $E_i$       | V                  |

|-------------------|-------------------------------------------------------|--------------------|

| Ψ                 | electrostatic potential                               | V                  |

| $\Psi_s$          | surface potential, referenced to the source           | V                  |

| $p_s$             | hole surface concentration                            | $cm^{-3}$          |

| $p_{\nu}$         | density of holes in the valence band                  | $cm^{-3}$          |

| q                 | electron charge                                       | С                  |

| $Q_B$             | bulk silicon charge                                   | C/cm <sup>2</sup>  |

| $Q_c$             | junction capacitance charge integrated over voltage   | $C/cm^2$           |

| $Q_D$             | depletion layer charge                                | $C/cm^2$           |

| $Q_f$             | oxide fixed charge                                    | $C/cm^2$           |

| $Q_{ii}$          | interface trap charge                                 | $C/cm^2$           |

| $Q_{ol}$          | oxide bulk trapped charge                             | C/cm <sup>2</sup>  |

| $Q_n$             | n-ch inversion layer charge                           | $C/cm^2$           |

| $Q_p$             | p-ch inversion layer charge                           | $C/cm^2$           |

| $Q_t$             | total of oxide and interface trapped charge           | $C/cm^2$           |

| $Q_s$             | silicon surface charge                                | $C/cm^2$           |

| $R_{mn}$          | normalized current ratio to calculate m,n             |                    |

| $R_S$ , $R_D$     | source, drain series resistance                       | Ω                  |

| S                 | slope for device lifetime extrapolation               |                    |

| τ                 | aging lifetime for $10\% g_m$ degradation             | minutes            |

| $\theta_s$        | high vertical field surface mobility reduction factor | $V^{-1}$           |

| $t_{ox}$          | gate oxide thickness                                  | cm                 |

| T                 | absolute temperature                                  | °K                 |

| $\mu_{n,eff}$     | effective n-channel mobility                          | $cm^2V^{-1}s^{-1}$ |

| $\mu_{p,eff}$     | effective p-channel mobility                          | $cm^2V^{-1}s^{-1}$ |

| $\mu_o$           | low field channel mobility                            | $cm^2V^{-1}s^{-1}$ |

| $v_{th}$          | thermal velocity of carriers                          | $cm \cdot s^{-1}$  |

| $V_D$             | drain voltage                                         | V                  |

| $V_G$             | gate voltage                                          | V                  |

| $V_{\mathcal{S}}$ | source voltage                                        | V                  |

| $V_{BS}$          | bulk to source voltage                                | V                  |

| $V_{DD}$          | operating voltage                                     | V                  |

| $V_{DS}$          | drain to source voltage                               | V                  |

|                   |                                                       |                    |

| $V_{GS}$     | gate to source voltage  | V  |

|--------------|-------------------------|----|

| $V_{FB}$     | flat band voltage       | v  |

| $V_{in}$     | n-ch threshold voltage  | v  |

| $V_{tp}$     | p-ch threshold voltage  | v  |

| $V_T$        | thermal voltage (kT/q)  | v  |

| $W, W_{eff}$ | effective channel width | cm |

| $x_{jn}$     | n-ch junction depth     | cm |

| $x_{ip}$     | p-ch junction depth     | cm |

#### **ABSTRACT**

In the continuing scaling of the CMOS (Complementary Metal Oxide Semiconductor) transistors to achieve higher circuit performance, density and functional complexity, the device physicists and process technologists are faced with the challenges of the high field phenomena in these devices due to the shear reduction in device dimensions, both laterally and vertically. The shorter channel length in an MOS device causes the device to be susceptible to subthreshold leakage, or in the extreme case, punch-through, if the device structure is not designed properly by increasing the doping concentration in the channel to suppress the bulk and surface conduction paths. At the same time, the source and drain junction depths must be reduced. The higher concentration of the doping impurity in the channel will lead to mobility degradation in the inversion layer, lower junction breakdown, and increased hot carrier generation. The hot carrier generation in MOSFET transistors can cause degradation in performance due to interface states built-up at the drain and a reduction in transconductance and a shift in threshold voltage. The trapped charge in the gate oxide can lead to permanent oxide breakdown and drain junction leakage.

This dissertation aims at the detailed treatments of device and process design for submicron CMOS structures, with a strong emphasis on hot-carrier effects. The process and device modeling using numerical simulators is used to analyze and optimize device structures before the fabrication process. The devices are fabricated with a state-of-the-art processing technology. Experimental results from submicron devices are presented to verify the analysis and modeling. The gate oxide thickness of the devices is in the range of 125 Å to 210 Å, and the effective channel length is in the range of 0.4 to 1.0 µm. A comprehensive device and process characterization methodology is presented. New phenomena in small devices, such as reverse subthreshold swing and reverse short channel effects, are reported. An experimental procedure to determine the optimum off current with respect to channel length and leakage requirements at different temperatures is presented.

For hot carrier considerations, the NMOS LDD drain was designed with an optimized dose and a spacer width, and verified with substrate current and aging results. The work on the hot carrier generation process in the MOS device leads to an improved model to predict substrate current as a function of the applied drain voltage. Therefore, the lifetime prediction is improved for a MOS device, which operates at a lower drain voltage than the accelerated stress voltage. The physical understanding of the interface state built-up during device aging is analyzed using the method, based on the physics of subthreshold conduction and the extension of drain depletion region, to extract the spatial distribution of interface state density along the channel from the drain end. The distribution of interface states as a function of time and space uncovers the dynamics of charges built-up during device stressing. This method can be implemented to routinely monitor device aging during development and in manufacturing. Predicting device lifetime using substrate current extrapolation for different channel length devices can lead to errors. The device lifetime prediction using substrate current for the same channel length devices is recommended for a more consistent in channel electric field of the devices. A new model to relate peak substrate current to the drain voltage can also be used to predict the device lifetime at operating voltage, using an inverse of the square-root of the drain voltage. The substrate current measured at operating voltage is also used to detect process variation conditions in etching the gate sidewall spacer in manufacturing. However, the ultimate objective of the study of device degradation is to apply these predictions to actual circuits. In this light, a simple analysis of substrate current generated during switching in an CMOS inverter is used to predict the lifetime.

The uniqueness of this work is in the treatments of device design, process integration, device reliability and circuit design techniques as an integral system, in which, each area is interrelated to each other. A combined solution from the above specialized areas for the high field effects in small devices should be explored for submicron technologies. The work in this dissertation also serves to bridge the gap between device physics theory and its use in the design and characterization of the CMOS devices in the semiconductor industry.

#### Chapter 1

#### INTRODUCTION

With the rapid progress in the Silicon VLSI and ULSI (Very and Ultra Large Scale Integration) technology and its applications in the past 3 decades, it is instructive to review several key breakthroughs during this period in the areas of device invention, technology advancements, and the circuit and system applications. This chapter starts with a review of the historical events which have led to the present progress in silicon integrated circuits. Special emphasis is devoted to modern CMOS technology since it is the driving force behind device scaling to achieve higher level of circuit performance, density, and more complex functions. However, the emerging BiCMOS technology in which bipolar and CMOS devices are integrated on the same silicon wafer promises to be the trend for the future.

#### 1.1 HISTORICAL REVIEW

Let us first review the major scientific inventions in the areas of semiconductor device physics, material and processing techniques, and apply this silicon technology to the development of complex integrated circuits. We shall divide the semiconductor revolution into three periods: The first period spanned the early discoveries and inventions in device structures, basic material processes, and the fundamental device physics theory. The second period began with the invention of the integrated circuit in which active devices (transistors) and passive components (resistors and capacitors) are integrated on a monolithic semiconductor substrate. It was in this period that the thrust for miniaturization or scaling to smaller devices and interconnect dimensions became prominent. This period included many processing breakthroughs and characterization techniques that overcame earlier difficulty in device fabrication. The third period focused on applications, and started with the development of the 1-transistor DRAM (Dynamic Random Access Memory) integrated circuits, followed by the 256-bit SRAM (Static RAM) and a 4-bit microprocessor at Intel Corp.. We are now over 2 decades into this period, and the thrust for scaling feature sizes is continuing at a very rapid pace. This trend in silicon technology will take us well into the information age of the 21<sup>th</sup> century, and may only be supplanted by fields such as

bioelectronics, artificial intelligence, and neural networks.

Let's step back and see how all this began.

#### 1.1.1 Major Inventions And Breakthroughs in Device Structures and Theory

The major inventions that led to the present state-of-the-art in MOS technology can be traced back to 1928 with the patent disclosure by Lilienfeld<sup>[1]</sup> of the field-effect modulation of the conductance of Copper Sulfide (CuS) by an Al plate on top of an  $Al_2O_3$  insulator. This is now considered the first field effect device or Field Effect Transistor (FET). The idea was not implemented until 1960, when D. Kahng and M. Atalla of Bell Telephone Laboratories (BTL) demonstrated the enhancement-mode inversion-layer Metal Oxide Semiconductor Field Effect Transistor (MOSFET) using  $SiO_2$  as the insulator and Si as the semiconductor material. Between these two events, several other important inventions took place in areas of device physics, processing technology and materials that all contributed to the MOS and bipolar integrated circuit evolution.

#### 1.1.1.1 The Bipolar Transistor

The most famous invention that revolutionized the electronic industry, the modern style of living, and the information age, is the discovery of the transistor (transfer-resistor) at Bell Laboratories in December 1947 by Bardeen and Brattain. The first transistor was in the form of a point-contact. This structure was built from a plate of n-type germanium and two line-contacts of gold supported on a mylar wedge. The n-type Ge material is referred to as "base" in this structure, and the emitter and collector are referred to as the emitting and collecting functions of their respective terminals. According to W. Shockley, the birth of the transistor has been accepted as the day before Christmas Eve (December 23) of 1947, within the Bell Labs research community, although the rest of the world did not know until the announcement and first public demonstration of the discovery on June 30, 1948. Shockley felt some frustration by not being one of the inventors despite the efforts he had started eight years earlier. This motivated Shockley to produce more than 90 patents related to the transistor. Among these works was the concept of the junction transistor recorded on January 23, 1948 in Shockley's notebook, for which the patent was filed in June, 1948. 1948 was an important year in device physics and

structure for the junction transistor. Shockley introduced many concepts that are still being used. These concepts and physical understanding include IMREF (or quasi-Fermi level), heterojunctions with wide energy band gap to increase emitter efficiency, and multi-layer structures for modulation. These last two important concepts are now employed in GaAs technology for HBT (Heterojunction Bipolar Transistor) and HEMT (High Electron Mobility Transistor) devices. The idea of minority carrier injection was a major milestone in understanding the physics of transistor action. The theory of p-n junctions and transistors was published in a classic paper in 1949. During the early part of the 1950's, when the discrete transistor technology was licensed to the industry, more device concepts and theory were developed at Bell Labs. In 1952, Shockley, Read and Hall developed the recombination theory which greatly helped in understanding the generation-recombination processes of electron-hole pairs in semiconductor bulk and surface. This theory has had a direct effect in understanding the defect centers and the processes which control the reverse junction leakage current in p-n junction, bipolar and MOS devices.

#### 1.1.1.2 The Field Effect Transistor Concepts

With the advancement in theory and technology know-how during the early days of transistor, the 1953 JFET (Junction FET) was built at Bell Laboratories by Dacey and Ross. <sup>[7]</sup> The JFET operates on the principle of bulk conduction modulation by varying the depletion width of the 2 junctions biased in the reverse mode. The application of this device is limited to operational ampliers and other analog circuits. In this same year, Brown<sup>[8]</sup> at Bell Labs studied the inversion layer, or channel, which conducts the leakage current in the base surface of a germanium *npn* transistor. This work served as the basic foundation for understanding the MOS device operation. It was noted that the conductance between the emitter and collector of an n-p-n bipolar device was much larger than expected with the floating base. Brown<sup>[8]</sup> proposed a model and experimentally verified the existence of a channel layer bridging the 2 p-n junctions of the emitter and collector. More important to the inversion layer observation, Ross<sup>[9]</sup> in 1955 proposed that the inversion layer can be induced electrostatically by a control electrode placed in the vicinity of the channel region. Ferroelectric material was used to separate the electrode and

the floating base. Ross further proposed the channel could be controllably turned on and off as the potential on the gate electrode is applied or removed. An impedance meter connected between collector (or drain) and emitter (or source) can monitor whether the channel is formed. This is the first form of Read Only Memory (ROM) cell. The use of a ferroelectric as a gate dielectric material, which proved impractical at the time, was not pursued.

In 1959, Atalla<sup>[10]</sup> suggested that thermally grown  $SiO_2$  on Si single crystal substrate be used as the gate insulator. This concept led to the first successful fabrication of modern Metal Oxide Semiconductor Field Effect Transistor (MOSFET) as shown in cross-section in Fig. 1-1.<sup>[11]</sup> It was this work and the outgrowth of the  $SiO_2$  works headed by Atalla <sup>[12]</sup> at Bell Labs that paved the way for further studies in silicon dioxide for MOS device applications.

Figure 1-1. Cross-Section of a MOS Transistor

#### 1.1.1.3 Integrated Circuits Inventions

All of the inventions and developments described above took place at Bell Laboratories. However, the IC industry did not take off until the late 1950's with two major inventions that took place at Texas Instruments by Kilby (1958)<sup>[13]</sup> and Noyce at Fairchild Semiconductor (1959).<sup>[14]</sup> (Incidentally, Fairchild was spun off by Noyce, Moore and others from Shockley Transistor, Inc. founded by Shockley after his leaving the Bell Labs in 1957).

The initial motivation was to integrate active and passive discrete components together on a ceramic substrate when Kilby was with the CentraLab. [13] It was not until Kilby joined Texas Instruments in 1958 that the idea of integrating components on a single semiconductor material was invented. In Kilby's invention, the passive components were realized using the doped portion of semiconductor bulk for the resistors and p-n junctions for capacitors. The idea was first demonstrated by assembling the separate silicon components together. Subsequently, a phase-shift oscillator was integrated on a 0.4-in-square germanium wafer. A Digital flip-flop was also built using the same techniques. One year later, a planar silicon bipolar transistor technology was developed by Noyce at Fairchild, using similar integrated techniques. Although the inventor of integrated circuits often is a subject for controversial debate, both Kilby and Noyce are generally considered the forefathers of ICs for their discoveries.

To summarize this period, the three major inventions were the bipolar junction transistor, the demonstration of the silicon MOS transistor, and the integrated circuits. Although these are considered the major milestones, other basic processing technologies were developed along the way. Without these developments, the semiconductor technology would not have been in its present state.

#### 1.1.2 Technological Breakthroughs

The late 1940's and early 1950's was also a period of advancement in crystal growth and doping techniques, techniques needed to realize practical transistors. In 1950, a good p-n junction was formed by Teal, Sparks, and Buehler<sup>[15]</sup> by changing the doping of a melt as a crystal was grown. In 1952, Teal, Theuerer and Pfann developed the zone melting and crystal refining technique,<sup>[16]</sup> [17] which was essential for growing a purified and low intrinsic defect density material. Along with his other inventions, Shockley also pioneered the idea of using ion implantation to selectively dope a region of a semiconductor wafer.<sup>[18]</sup> This technique has become the standard doping method for fabricating VLSI circuits.

As mentioned earlier, the efforts in silicon dioxide growth led to the fabrication of the MOSFET transistor. The use of silicon dioxide as a diffusion mask by Frosch and Derrick, [19] in 1957 was also considered a technological breakthrough. This technique has been used to

selectively dope a silicon area by a patterned oxide layer, which blocks the dopant where it is not needed and allows the dopant to enter areas in which a diffused dopant is desired. The Epitaxial Layer used for bipolar junction transistor was proposed in 1959 by Theuerer. The epitaxial layer, used as part of the collector, is grown on a patterned highly doped buried layer. The buried layer reduces the collector series resistance, improving the transistor speed.

In order to understand the property of the Si-SiO<sub>2</sub> interface which was very difficult to control in the early days of MOS device fabrication, Terman <sup>[22]</sup> at Stanford Uninversity developed the Capacitance-Voltage (C-V) Technique in 1961. (This work was suggested and guided by J. Moll.)<sup>[23]</sup> This method has aided in the understanding of the charges present in a MOS system. This technique, and its derivatives, together with silicon oxidation techniques<sup>[24]</sup> have resulted in the Si-SiO<sub>2</sub> system being the most extensively studied interface in solid-state science. Another problem associated with silicon dioxide is contamination with sodium ions which drift in the oxide bulk and cause a shift in the flat-band voltage of an MOS capacitor and translates into a threshold voltage shift in the MOS transistor. This problem was studied by Snow et al.<sup>[25]</sup> at Fairchild. Kerr<sup>[26]</sup> at IBM in 1964 used a phosphorus-silicate-glass to stabilize the sodium drift in the oxide and to getter heavy impurities in silicon material, reducing junction leakage.

Kooi<sup>[27]</sup> at Philips contributed to the understanding of interface traps and most importantly the Local Oxidation (LOCOS) technique for device isolation, in which a layer of silicon nitride is used as an oxidation mask during the growth of field oxide. The invention of the poly-silicon gate by Kerwin et al <sup>[28]</sup> at Bell Labs led to the self-aligned gate-to-source-drain MOSFET structure. This structure reduces the overlap capacitance and avoids the stringent alignment requirements of an aluminum gate MOS transistor. The LOCOS isolation technique and polysilicon gate structures have remained the mainstream technology for fabricating MOS devices.

On the technology integration side, in 1963 Wanlass and Sah<sup>[29]</sup> of Fairchild Semiconductor were the first who suggested the use of n and p channel MOSFET devices in low power logic circuits such as inverter, NOR gate, and flip-flop. However, the NMOS and PMOS

devices were fabricated on two different types (p and n respectively) of silicon wafers by a planar diffusion process. White and Cricchi were the first who successfully fabricated CMOS devices on a single substrate epitaxial wafer. [30] Kahng and Sze[31] in 1967 proposed MNOS (Metal Nitride Oxide Semiconductor) device structures that can change the threshold voltage of an MOS device upon applying high enough potential onto the gate to induce charge injection. This structure has led to the field of non-volatile memory, presently known as EPROM (Electrically Programmable Read Only Memory), and EEPROM (Electrically Erasable PROM). The present mainstream applications in integrated circuits stemmed from the 2 circuits developments in late 1960's, which will be discussed in the next section.

#### 1.1.3 Circuit and System Applications Driven Technology

From the invention of integrated circuits until late 1960's, most applications focused on linear applications such as operational amplifiers, oscillators, comparators. During this period, digital applications included logic gates, flip-flops, counters, decoders, adders, etc.. This period constitutes an era known as SSI (Small Scale Integration) and MSI (Medium Scale Integration), when the transistor count on a given chip was in the range of tens to hundreds.

The two circuit concepts that fueled the drive for device scaling are the 1-Transistor DRAM (Dynamic Random Access Memory) cell proposed by Dennard<sup>[32]</sup> of IBM, and the 6-Transistor (or 4-T with resistor load) SRAM cell. The DRAM cell is comprised of one MOS transistor serving as an access device to a storage capacitor used as a memory element. This basic circuit configuration is a foundation for the modern day high density DRAM chip. The LSI era dawned with products like the 16K DRAM, the 8-bit microprocessors and gate array where the transistor count was in the range of few thousand to 100 thousand. Since the early days of integrated circuits application, the growth of the semiconductor industry has been astronomical. From the Small Scale level of integration (SSI) of TTL logic gates with dozens of transistors and features sizes greater than 10 μm in the early 1960's, [33] the level of integration has reached the level at this writing of integrating more than 36 million device components on a 16 megabit DRAM chip with minimum feature sizes of 0.5 micrometer. [34] An experimental 64Mb DRAM chip designed with 0.3μm feature size using e-beam lithography, operating at 1.5V supply voltage has been

#### successfully demonstrated. [35]

The progress of down scaling in device geometry and minimum feature size can be monitored by the introduction of high density DRAM's and SRAM's. Memory is usually the first product to benefit from device scaling. It is estimated that DRAM density quadruples every 2.5 years (Figure 1-2).

Figure 1-2. DRAM and SRAM density vs the year of introduction.

The trend is the same for Static Random Access Memory (SRAM) but the memory capacity of a state of the art SRAM is typically one fourth of the DRAM capacity. Memory products are considered technology drivers because circuit regularity and ease of failure mode analysis help the technologist 'fine-tune' the fabrication process.

Other applications, such as microprocessors and custom digital circuits, typically follow the lead of memory technology, even though DRAM technology is not directly compatible with logic circuit applications. Power delay products of logic gates have dropped by more than 6 decades to reach 10<sup>-1</sup> pJ in 1990 as a result of device scaling as shown in Figure 1-3. The design of logic custom integrated circuits also drives the active software development for CAD (Computer Aided Design) tools that help to integrate millions of transistors on a logic chip.<sup>[36]</sup>

Figure 1-3. Power-Delay Product per inverter gate versus year.