The Preserve: Lehigh Library Digital Collections

## Characterization of SONOS nonvolatile semiconductor memory (NVSM) devices for space and military applications.

#### Citation

Wrazien, Stephen J. - Lehigh University. Characterization of SONOS Nonvolatile Semi-conductor Memory (NVSM) Devices for Space and Military Applications. 2005, https://preserve.lehigh.edu/lehigh-scholarship/graduate-publications-theses-dissertations/theses-dissertations-97.

Find more at https://preserve.lehigh.edu/

This document is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion by an authorized administrator of Lehigh Preserve. For more information, please contact <a href="mailto:preserve@lehigh.edu">preserve@lehigh.edu</a>.

# Characterization of SONOS Nonvolatile Semiconductor Memory (NVSM) Devices for Space and Military Applications

by

Stephen J. Wrazien

A Dissertation

Presented to the Graduate and Research Committee

of Lehigh University

in Candidacy for the Degree of

Doctor of Philosophy

in

**Electrical Engineering**

Lehigh University

May 2005

UMI Number: 3167087

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform 3167087

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 This dissertation is approved and recommended for acceptance as a Dissertation in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering.

<u>April 25 th 2005</u>

Date

Dissertation Advisor

Accepted Date

Committee Members:

Marvin H. White

Dennis A. Adams

1. Jaccodine

Svetlana Tatic-Lucic

To my parents, Barbara and Carl,

my brother, Dan,

my girlfriend, Lorie,

and my friends,

for all of their love and encouragement.

And to the 2004 Boston Red Sox

#### Acknowledgements

Thinking back on all of the experiences and events over the past few years of my graduate studies, it's amazing how many people have contributed to this degree. Whether it was working with me for a summer, collaborating on a paper, teaching me device physics, demonstrating processing techniques, or just encouraging me to keep going because I was so close to finishing and what a great achievement it will be once I'm finished, without this support and encouragement, this dissertation would not exist.

First, I would like to thank my advisor and mentor, Dr. Marvin White, for the opportunity to study at the Sherman Fairchild Lab as both an undergraduate and a graduate student. His financial support, technical expertise, and passion for innovative device research have fueled this research. The members of my Ph.D. committee, Dennis Adams, Dr. Ralph Jaccodine, and Dr. Svetlana Tatic-Lucic, have provided invaluable insight into device research and helped shape this dissertation. I would especially like to thank Dennis Adams, who has collaborated with our research group over the course of my studies, provided myself an internship at the Northrop Grumman Corporation, and has always supported my graduate and professional careers.

The faculty, staff, and students of the Sherman Fairchild Center have made the lab an innovative and stimulating research environment. I would never have been able to fabricate working devices without the expertise and patience of Raymond Filozof. His dedication to excellent processing techniques and to helping his students have made semiconductor processing at the lab an enjoyable and rewarding experience. Dr. Floyd

Miller has provided insights into fabrication techniques as well as introduced me to the art of SEM imaging. Mrs. Linda Dreisbach has provided constant support, ensuring that the administrative side of graduate research is always under control.

I would like to thank my fellow graduate students; Themis Afentakis, Jiankang Bu, Ta-Ko Chuang, James Fuerherm, Abbas Jamshidi-Roudbari, Gaoshan Jing, Joel Krayer, Santosh Pandey, Huiling Shang, Matias Troccoli, Yu "Richard" Wang, Xiaonan "Stephen" Wang, Yi Yao, Yu "Anne" Zeng, Wenyue Zhang, Yanli "Esther" Zhang, and Yijie "Sandy" Zhao, for their technical expertise and friendship. I'd especially like to thank; Matias, who has been a good friend and put up with living with me for the past 2 years, Gaoshan, a fellow member of Red Sox Nation, Joel, with whom I have enjoyed many music-related and random discussions, and Santosh, Anne, and Sandy, who have provided me with mentorship and friendship since day one at the lab. I'd also like to thank all of the summer students I have worked with on the SONOS project over the years (in chronological order); Jon Faul, Joel Krayer, Bilal Khan, Rajiv Mehrotra, and Wayne Miller. In addition, Andy Bronczyk, who made the summer of 2004 one of the most enjoyable in memory.

Huge thanks to my family and all of my friends who have supported me all along. Special thanks to my Mom, Dad, Dan, and my girlfriend Lorie, who have given me overwhelming love and encouragement. I'd also like to thank Eric, Adam, and Steve for providing me with many more than memorable non-research moments.

Thanks to the Northrop Grumman Corporation, the Army Space and Missile Defense Command, the Sherman Fairchild Foundation, and the National Science Foundation for their financial support.

v

#### **Contents**

| Ackn   | owledg | gements                                                   | iv |

|--------|--------|-----------------------------------------------------------|----|

| List o | f Tabl | es                                                        | ix |

| List o | f Figu | res                                                       | x  |

| Abstr  | act    |                                                           | 1  |

| 1.     | Intro  | oduction to Non-Volatile Semiconductor Memory (NVSM)      | 3  |

|        | 1.1    | Space and Military Electronic Systems                     | 4  |

|        | 1.2    | NVSM Technologies for Space and Military Applications     | 10 |

|        |        | 1.2.1 Floating Gate                                       | 11 |

|        |        | 1.2.2 SONOS                                               | 14 |

|        |        | 1.2.3 NROM <sup>TM</sup>                                  | 16 |

|        |        | 1.2.4 Novel Concept NVSM's                                | 21 |

|        | 1.3    | Scope of the Dissertation                                 | 25 |

| 2.     | Char   | nnel Initiated Secondary Electron Injection (CHISEL)      |    |

|        | in SN  | NROM Transistors                                          | 28 |

|        | 2.1    | CHISEL Injection in Floating Gate Transistors             | 28 |

|        | 2.2    | CHISEL Injection in SNROM Transistors                     | 31 |

|        |        | 2.2.1 Modeling SNROM Threshold Voltage Shift during       |    |

|        |        | CHISEL Injection                                          | 35 |

|        |        | 2.2.2 SNROM CHISEL Impact Ionization Current              | 41 |

| 3.     | Mod    | eling Density of Traps in Oxynitride Charge Storage Films |    |

|        | in Sc  | aled SONOS Transistors                                    | 43 |

|    | 3.1       | Historical Perspective                              | 44 |

|----|-----------|-----------------------------------------------------|----|

|    | 3.2       | Trap Density Modeling                               | 45 |

| 4. | SONO      | OS Device Design and Fabrication                    | 53 |

|    | 4.1       | Threshold Voltage Adjust Implant                    | 53 |

|    | 4.2       | SONOS Gate Stack                                    | 56 |

|    | 4.3       | Polysilicon Gate Etch                               | 57 |

|    | 4.4       | Short Channel Transistor Fabrication                | 60 |

| 5. | Electi    | rical Characterization Techniques                   | 63 |

|    | 5.1       | Programming                                         | 65 |

|    | Retention | 69                                                  |    |

|    |           | 5.2.1 High Temperature Electrical Measurement Setup | 70 |

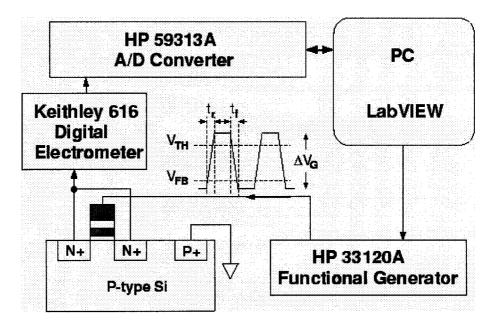

|    | 5.3       | Charge Pumping                                      | 74 |

|    |           | 5.3.1 Square Waveform                               | 74 |

|    |           | 5.3.2 Triangular Waveform                           | 77 |

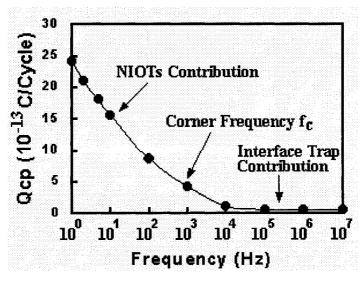

|    |           | 5.3.3 Variable Frequency                            | 79 |

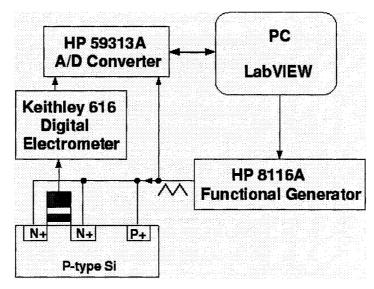

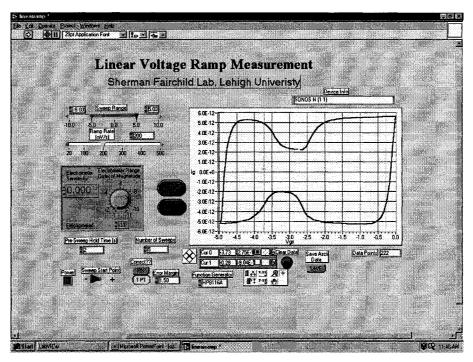

|    | 5.4       | Quasi-Static Capacitance (Linear Voltage Ramp)      | 82 |

| 6. | Chara     | acterization of Scaled SONOS/NROMTM/SNROM           |    |

|    | Devic     | es for Space and Military Applications              | 86 |

|    | 6.1       | Programming Efficiency                              | 88 |

|    | 6.2       | Extrapolating Memory Retention                      | 94 |

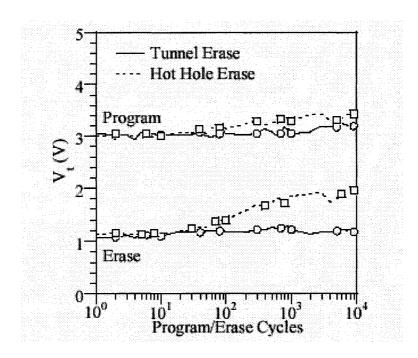

|    | 6.3       | Endurance                                           | 10 |

|    | 6.4       | Ideal NVSM for Space and Military Applications      | 10 |

| 7.    | Conc     | lusions                                              | 113 |

|-------|----------|------------------------------------------------------|-----|

|       | 7.1      | Characterization and Modeling of CHISEL Injection in |     |

|       |          | SNROM NVSM Transistors                               | 113 |

|       | 7.2      | Predicting 10-Year SONOS Data Retention              | 114 |

|       | 7.3      | Short-Channel SONOS Transistor Fabrication           | 114 |

|       | 7.4      | Characterizing the Ideal NVSM for Space and          |     |

|       |          | Military Applications                                | 115 |

|       | 7.5      | Future Research Recommendations                      | 116 |

| Refer | ences    |                                                      | 117 |

| Appe  | ndices   |                                                      |     |

| A. SC | ONOS     | Device Fabrication Sequence                          | 125 |

| В. М  | [easure  | ment Procedures                                      | 130 |

| C. Fa | abricati | ion Simulations                                      | 137 |

| D. E  | rbium-   | Doped CMOS Capacitors (Proposal)                     | 145 |

| E. La | abVIEV   | W Program – 4145 Plot Download Program               | 153 |

| Vita  |          |                                                      | 155 |

| Publi | cations  |                                                      | 156 |

#### **List of Tables**

| 1.1 | Summary of NVSM memory effects                | 4   |

|-----|-----------------------------------------------|-----|

| 1.2 | Space and military NVSM requirements          | 6   |

| 1.3 | SONOS vs. floating gate                       | 16  |

| 1.4 | Voltages for channel hot electron NROM™ write | 19  |

| 6.1 | Nitride-based NVSM programming voltages       | 91  |

| 6.2 | Summary of NVSM characteristics               | 111 |

| B.1 | Drain current vs. gate voltage connections    | 130 |

| C.1 | Implant drive-in anneal conditions            | 137 |

#### **List of Figures**

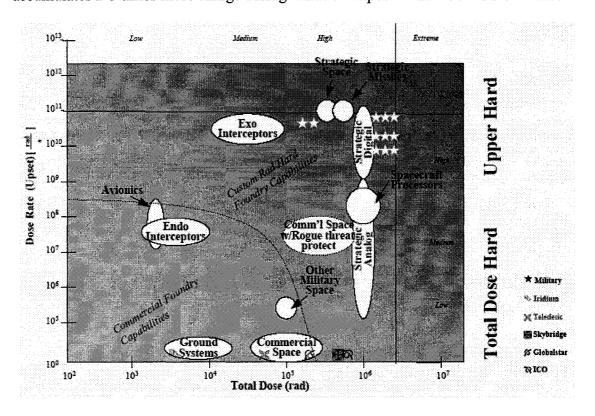

| 1.1  | Space and military NVSM requirements                   | 5  |

|------|--------------------------------------------------------|----|

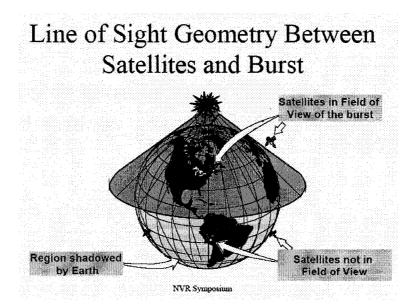

| 1.2  | Destruction of satellites from nuclear detonation      | 7  |

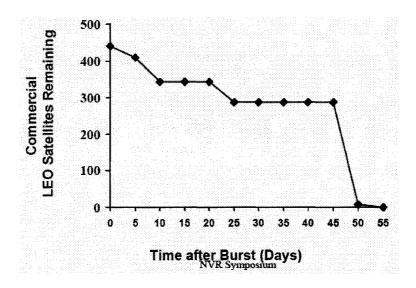

| 1.3  | Satellites remaining vs. days after nuclear detonation | 8  |

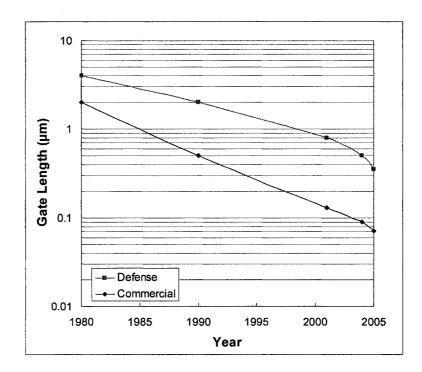

| 1.4  | Commercial and defense CMOS gate length scaling        | 9  |

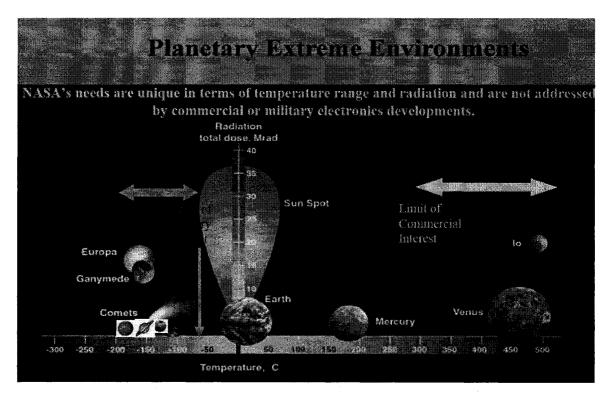

| 1.5  | Deep-space temperature and radiation requirements      | 10 |

| 1.6  | Flash memory (a) CHE write and (b) FN erase            | 12 |

| 1.7  | Floating gate leakage current vs. radiation exposure   | 13 |

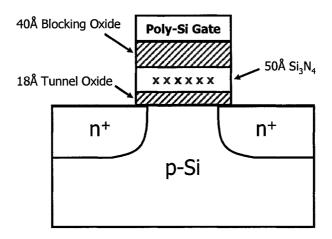

| 1.8  | SONOS vertical cross-section                           | 15 |

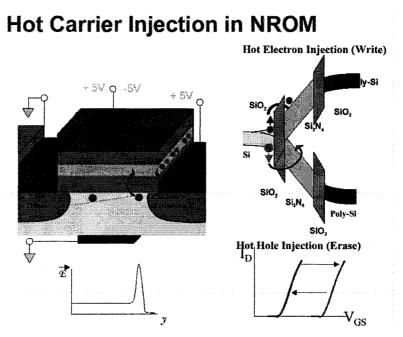

| 1.9  | NROM™ programmed with CHE/HHI                          | 17 |

| 1.10 | NROM™ multi-bit data storage                           | 18 |

| 1.11 | Endurance vs. cycling with CHE/tunneling and CHE/HHI   | 21 |

| 1.12 | Hysteresis of a ferroelectric capacitor                | 22 |

| 1.13 | Magnetic junction state read-out                       | 23 |

| 1.14 | TEM image of amorphous and crystalline GeSbTe film     | 24 |

| 1.15 | Memory effect of a PRAM                                | 25 |

| 2.1  | Cross-section of CHISEL in Floating Gate               | 29 |

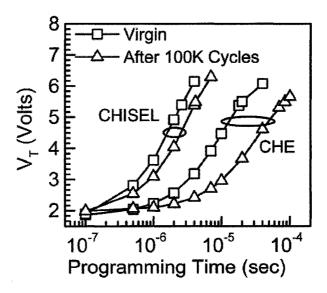

| 2.2  | Floating Gate programming with CHISEL/CHE              | 30 |

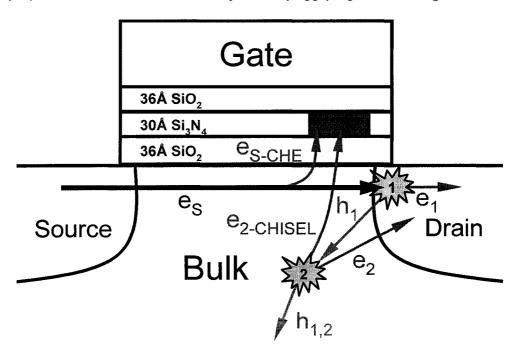

| 2.3  | Cross-section of CHISEL in SNROM                       | 32 |

| 2.4  | SNROM threshold voltage shift from CHISEL/HHI          | 33 |

| 2.5  | V <sub>TH</sub> vs. programming time with CHISEL/HHI                      | 34 |

|------|---------------------------------------------------------------------------|----|

| 2.6  | SNROM drain current during CHISEL write                                   | 36 |

| 2.7  | $V_{TH}$ shift extrapolated from channel current during CHISEL            | 37 |

| 2.8  | CHISEL charge injection region in SNROM gate                              | 38 |

| 2.9  | Charge trapping required to produce observed SNROM $V_{TH}$ shift $\dots$ | 39 |

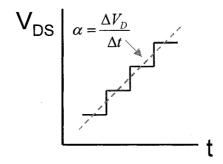

| 2.10 | Stepped drain voltage approximated as a ramped voltage                    | 40 |

| 2.11 | Current injected and trapped in the gate dielectric                       | 40 |

| 2.12 | Ionization current and slope of $V_{TH}$ change                           | 41 |

| 2.13 | Trapped and impact ionization currents                                    | 42 |

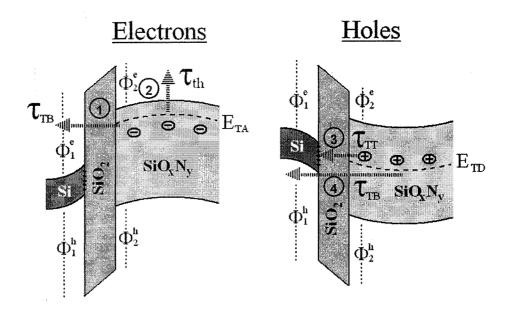

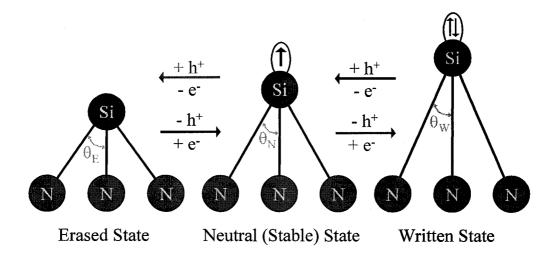

| 3.1  | SONOS charge loss mechanisms                                              | 46 |

| 3.2  | Amphoteric trap model in Si <sub>3</sub> N <sub>4</sub> film              | 47 |

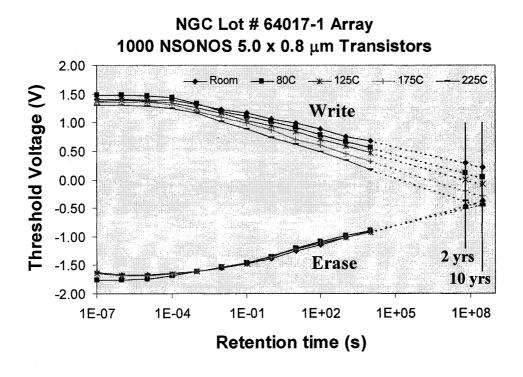

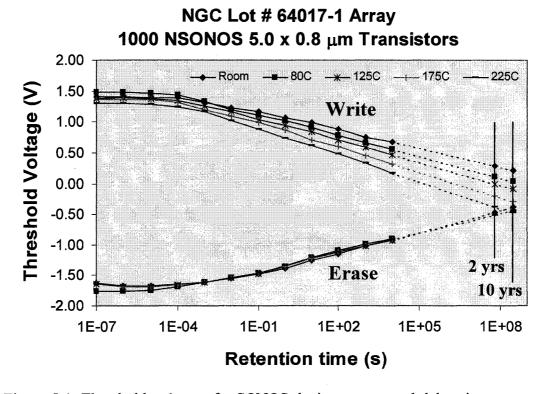

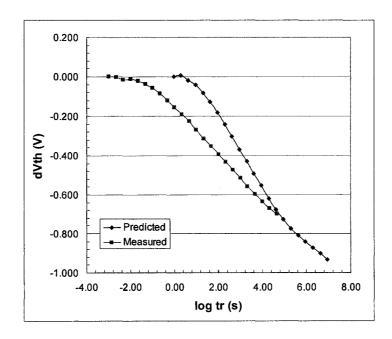

| 3.3  | SONOS retention at elevated temperatures                                  | 49 |

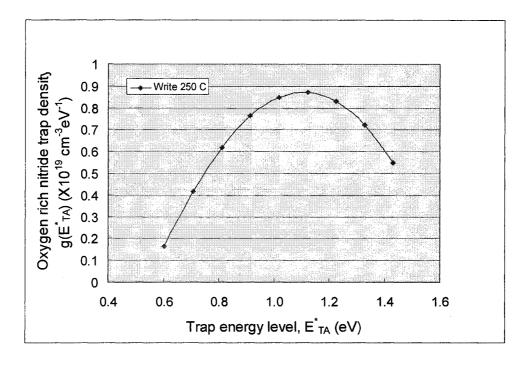

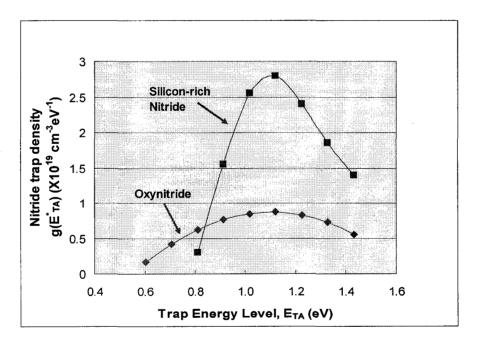

| 3.4  | Oxynitride trap density vs. trap energy                                   | 50 |

| 3.5  | Silicon-rich vs. oxynitride trap density                                  | 51 |

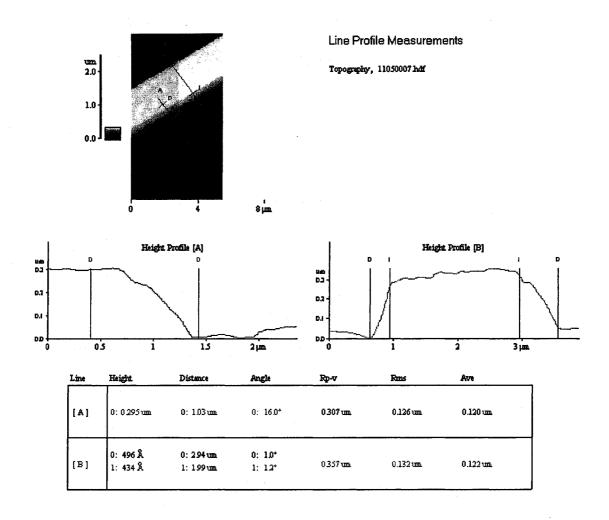

| 4.1  | AFM image of TRW etched polysilicon film                                  | 59 |

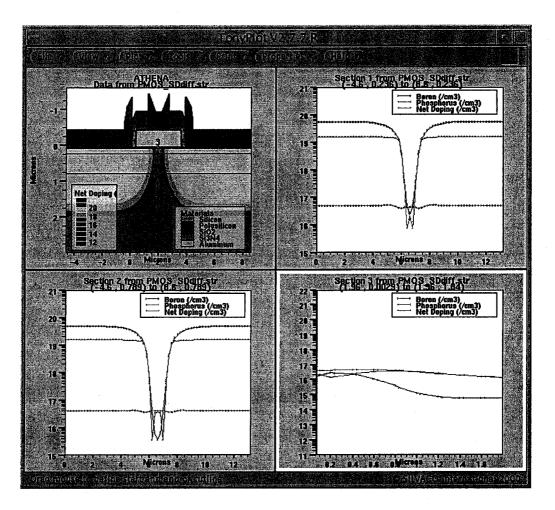

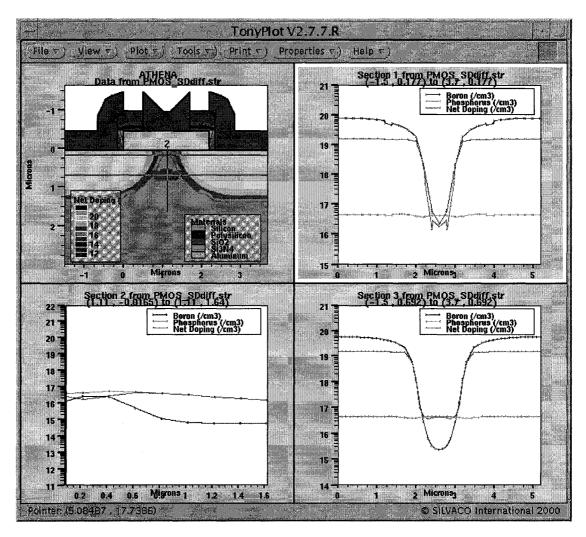

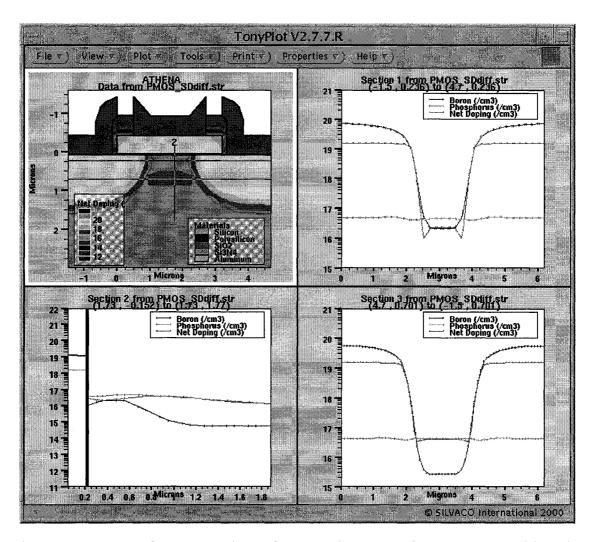

| 4.2  | Athena simulation of S/D drive-in anneal                                  | 61 |

| 5.1  | V <sub>TH</sub> read-out biasing for SONOS transistors                    | 64 |

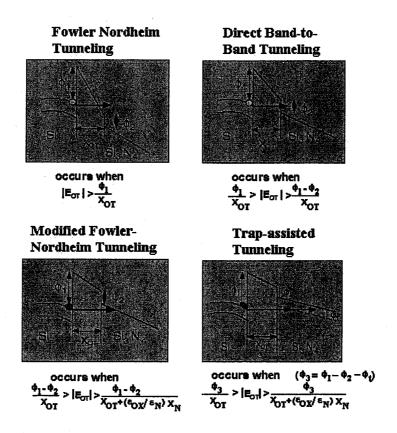

| 5.2  | Energy-band diagram during FN, DT, MFN, and TAT                           | 66 |

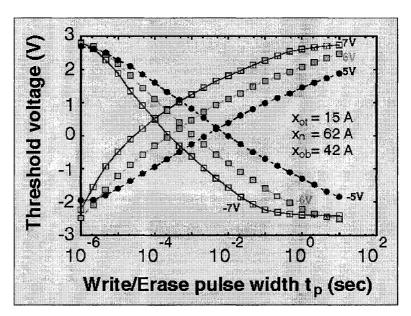

| 5.3  | SONOS programming at various gate voltages                                | 68 |

| 5.4  | SONOS retention at elevated temperatures                                  | 69 |

| 5.5  | SONOS wafer on hot chuck                                                  | 71 |

| 5.6  | Close-up of SONOS wafer on hot chuck                                      | 71 |

| 5.7  | Yamato DX 300 high temperature oven                            | 72  |

|------|----------------------------------------------------------------|-----|

| 5.8  | Front panel of DX 300 oven                                     | 73  |

| 5.9  | IC socket for high temperature measurements                    | 73  |

| 5.10 | Charge pumping electrical connections                          | 75  |

| 5.11 | Charge pumped vs. frequency                                    | 79  |

| 5.12 | Corner frequency vs. tunneling time constant                   | 81  |

| 5.13 | Linear voltage ramp electrical connections                     | 83  |

| 5.14 | LabVIEW <sup>TM</sup> program for LVR measurement              | 84  |

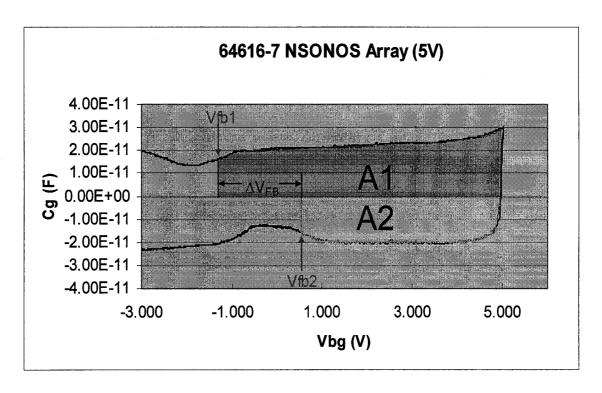

| 5.15 | LVR measurement with flat-band voltage shift                   | 85  |

| 6.1  | Off-state gate leakage current in SONOS transistor             | 86  |

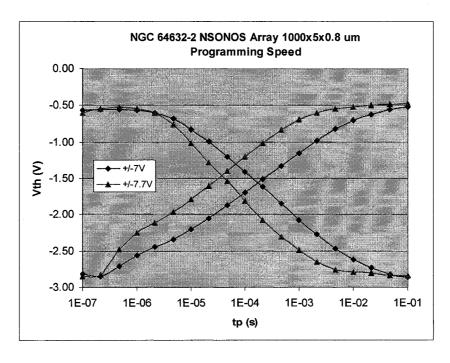

| 6.2  | MFN programming SONOS transistor at 7V and 7.7V                | 89  |

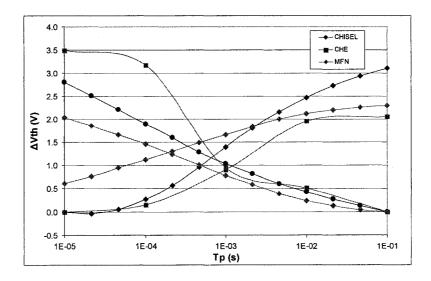

| 6.3  | Programming nitride-based NVSM's with CHE/CHISEL/MFN           | 91  |

| 6.4  | V <sub>TH</sub> shift from programming SNROM transistor        | 92  |

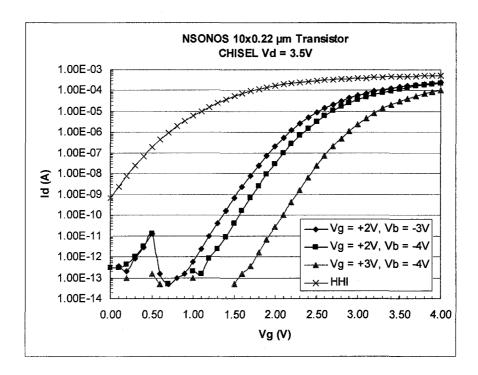

| 6.5  | SNROM drain current during CHISEL injection, varied bulk bias  | 93  |

| 6.6  | CHISEL injection point vs. varied bulk bias                    | 94  |

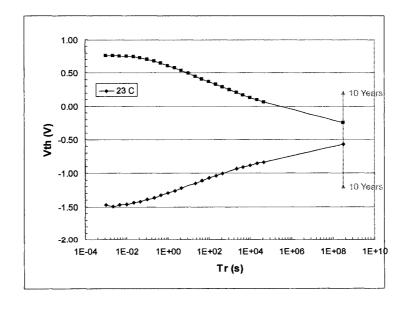

| 6.7  | Extrapolated SONOS retention at room temperature               | 95  |

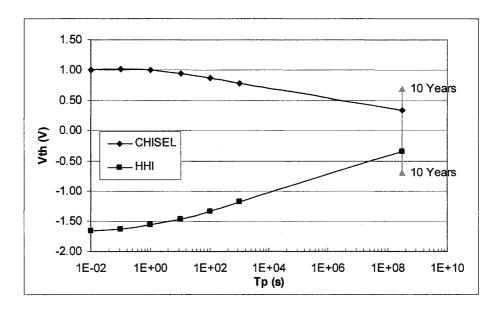

| 6.8  | SNROM retention programmed with CHISEL/HHI                     | 96  |

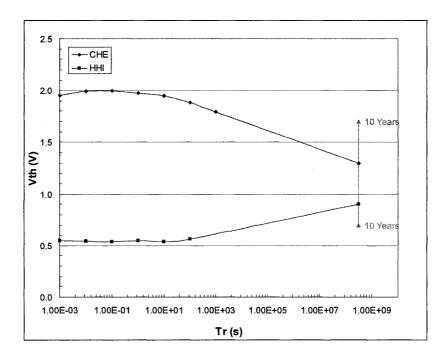

| 6.9  | NROM™ retention programmed with CHE/HHI                        | 97  |

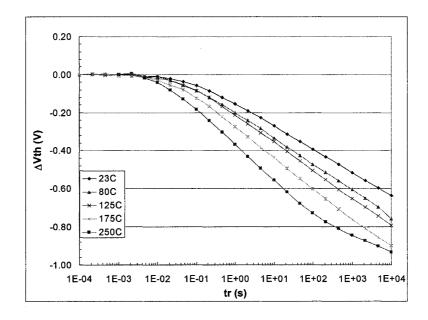

| 6.10 | V <sub>TH</sub> decay vs. time at various temperatures         | 98  |

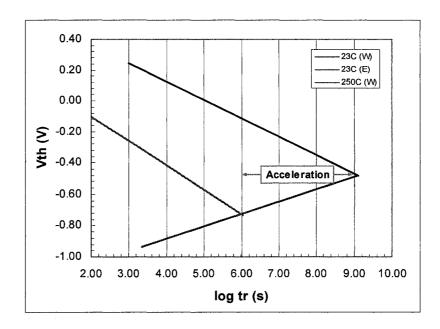

| 6.11 | Extrapolated retention at 23C and                              | 99  |

| 6.12 | Retention at 22C and predicted retention from 250C measurement | 99  |

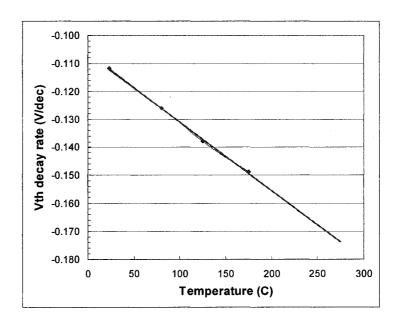

| 6.13 | V <sub>TH</sub> decay rate vs. temperature                     | 100 |

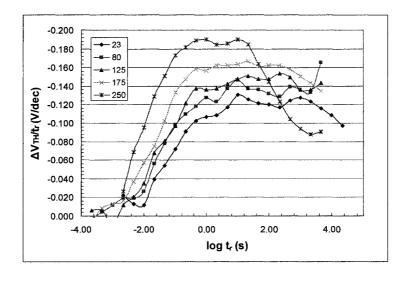

| 6.14 | $V_{TH}$ decay rate vs. log $t_r$ for various temperatures | 101 |

|------|------------------------------------------------------------|-----|

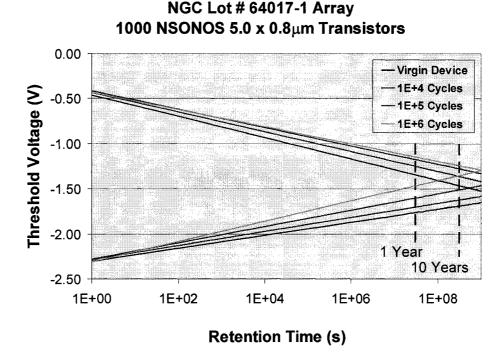

| 6.15 | NSONOS retention MFN tunneling                             | 102 |

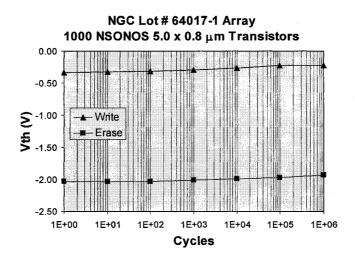

| 6.16 | Normalized D <sub>it</sub> for SNROM/NROM <sup>TM</sup>    | 105 |

| 6.17 | Initial memory window vs. stress                           | 106 |

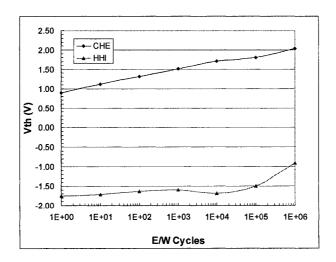

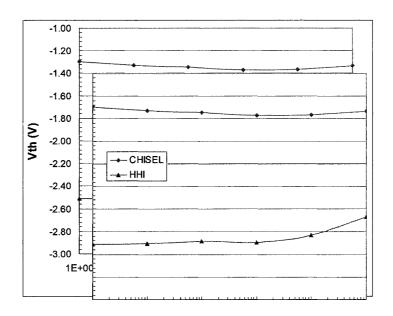

| 6.18 | NROM™ cycling with CHE/HHI                                 | 106 |

| 6.19 | SNROM cycling with CHISEL/HHI                              | 107 |

| 6.20 | Retention vs. time after various amounts of cycling stress | 108 |

| C.1  | SONOS channel after 120 min anneal at 1000C                | 143 |

| C.2  | SONOS channel after 160 min anneal at 1000C                | 144 |

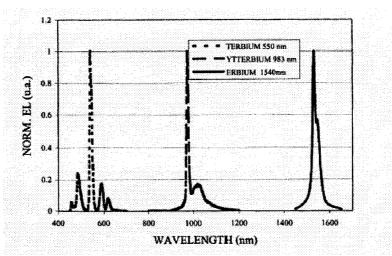

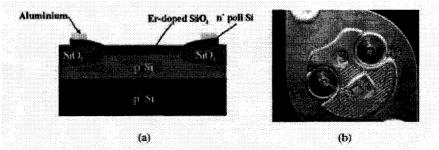

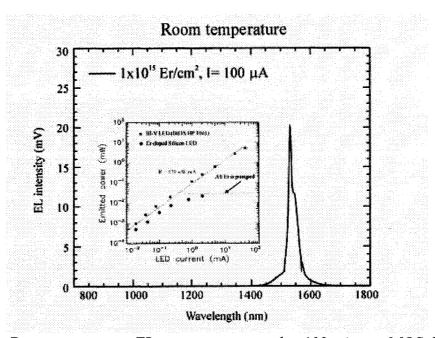

| D.1  | EL-spectrum of rare-Earth doped capacitors                 | 147 |

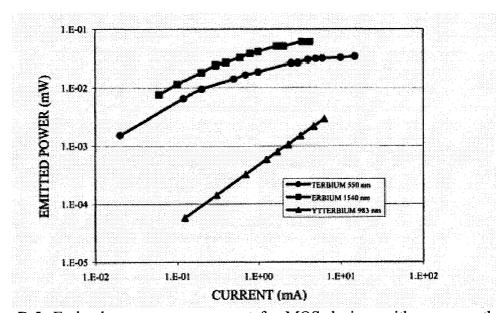

| D.2  | ST Microelectronics rare-earth doped emitters              | 148 |

| D.3  | Room temperature EL-spectrum at 100μA                      | 150 |

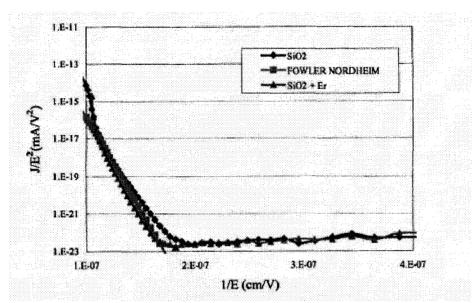

| D.4  | Fowler-Nordheim plots on doped capacitors                  | 151 |

| D.5  | Emitted power vs. current for doped capacitors             | 152 |

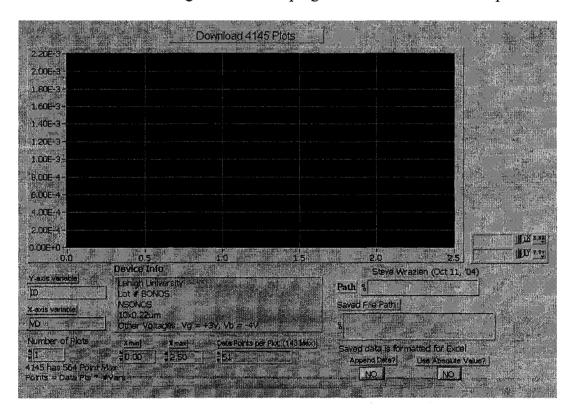

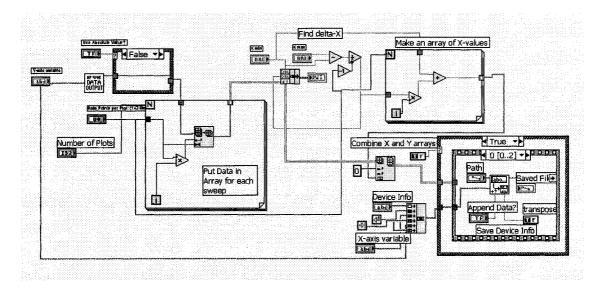

| E.1  | Front panel of LabVIEW <sup>TM</sup> program for 4145      | 153 |

| E.2  | Back panel of LabVIEW <sup>TM</sup> program for 4145       | 154 |

#### **Abstract**

The increasing miniaturization of portable electronics, application of electronic systems for deep-space exploration, and the advent of nuclear terrorism have created the need for a high-speed, low-power, high-density non-volatile semiconductor memory (NVSM) capable of long-term data retention under heavy radiation doses. This dissertation characterizes polysilicon-oxide-nitride-oxide-silicon (SONOS) transistors, and proposes, characterizes, and models a device derived from the SONOS technology, the substrate injection nitride based (SNROM) device, to meet the future requirements of space and military systems.

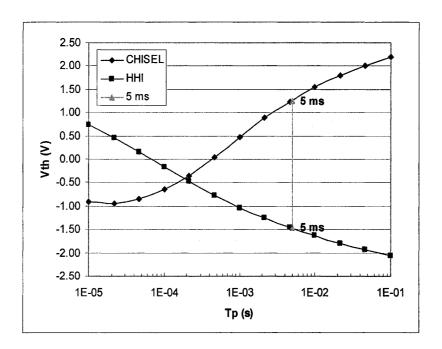

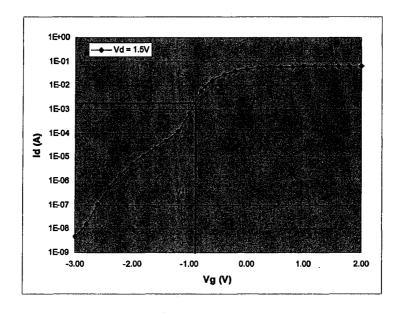

This research characterizes novel short-channel substrate-injection nitride-based (SNROM) transistors (10 x 0.22 µm) fabricated with a 36Å-thick tunnel oxide, 30Å silicon nitride, and a 36Å blocking oxide as the gate dielectric. The thick tunnel oxide prevents tunneling of electrons and holes through the gate dielectric and allows the transistor to be programmed using hot electron and hole injection. This research programs SNROM transistors to produce a 2-volt memory window. The device is written using channel initiated secondary electron injection (CHISEL) by applying 3V to the gate, 2.5V to the drain, and -4V to the bulk for 5ms. The device is erased using hot hole injection by applying -7V to the gate and 4V to the drain for 5ms. The programmed transistor surpasses the 10-year retention requirement with a 0.5V memory window at the 10-year mark. The CHISEL injection mechanism is characterized and

modeled by extrapolating the threshold voltage shift, trapped charge, and injected current, from the reduction in channel current during programming. In addition, the impact ionization current is measured at the drain terminal and correlated with the current injected into the ONO gate insulator.

Additionally, electrical characterization is performed on conventional SONOS transistors, with an emphasis on programming efficiency, endurance, and data retention. An acceleration factor is presented to linearly extrapolate 10-year retention from high temperature measurements. This dissertation demonstrates the ability of current conventional SONOS transistors to meet space and military system requirements and presents an innovative SNROM structure as a low-power, high-density NVSM for future applications.

#### Chapter 1

### Introduction to Non-Volatile Semiconductor Memory (NVSM)

Semiconductor memory devices have evolved greatly over the past 10 years. Semiconductor memory is used in a wide variety of applications from personal computer RAM, used to store information required to run software programs and operating systems, to complex electronic systems embedded in satellites and most recently, portable personal electronics. Traditionally, there have been two types of semiconductor memory, volatile and non-volatile memory. Volatile semiconductor memory (DRAM, SRAM) stores data in dense arrays and has quick access times and can endure up to 10<sup>12</sup> program/read cycles, but requires a power supply in order to retain data. Non-volatile semiconductor memory (NVSM) stores data in dense arrays with comparable access and programming times, but does not require power to retain data. However, the majority of NVSM's currently commercially available cannot withstand elevated programming (>10<sup>6</sup> write/erase cycles) and therefore cannot replace volatile semiconductor memory, such as DRAM personal computers [1].

Data is stored in semiconductor memory devices as a difference in turn-on (threshold) voltage, electrical resistance, or polarization, typically manifesting itself in a difference in read-out current when specific voltages are applied to the device. Writing the transistor will be referred to as a logic 'one', and erasing the device will be a logic

'zero'. The data must be retained by the NVSM for a minimum of 10 years.

The major NVSM's are floating gate (FG), discrete-trap (SONOS, NROM<sup>TM</sup>), and novel concept (FeRAM, MRAM, PRAM). These technologies differ in the method in which they sense a difference in memory state, see Table 1.1. This dissertation focuses mainly on the SONOS/NROM<sup>TM</sup> technologies, which store positive and negative charge (holes and electrons, respectively) in discrete traps in a silicon nitride film in the gate dielectric. The ability of NVSM's to retain information without a power

| NVSM          | Technology | Memory Effect                       |  |

|---------------|------------|-------------------------------------|--|

| Floating Gate | FG         | Conductive Gate                     |  |

| Discrete Trap | SONOS      | Si <sub>3</sub> N <sub>4</sub> film |  |

| Discrete Hap  | NROM       | Si₃N₄ film                          |  |

|               | MRAM       | Magnetic orientation                |  |

| Novel Concept | FeRAM      | Polarization                        |  |

|               | PRAM       | Physical state                      |  |

Table 1.1: Summary of current generation NVSM technologies and method employed to produce memory effect.

supply makes them ideal for use in portable electronics and space systems running off finite battery supplies. In addition, NVSM's which store charge in discrete traps are inherently radiation-hard and can withstand vast doses of radiation required for use in outer space where they are exposed to cosmic radiation and military systems where radiation from nuclear detonations is a concern.

#### 1.1 Space and Military Electronic Systems

Nonvolatile semiconductor memory is used in a variety of space and military applications. The NVSM technologies utilizing discrete charge trapping (SONOS) are

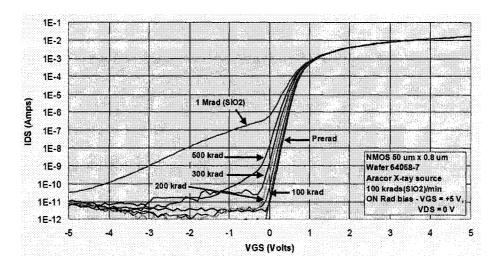

inherently radiation-hardened, due to their thin tunneling oxides. During radiation exposure, ions trap in the tunneling oxide of the transistor and shift the threshold voltage, causing leakage currents to flow while the device is in the off state. Thinner tunneling oxides trap fewer radiated ions and therefore do not suffer from excessive performance degradation due to radiation exposure. Floating gate memories cannot be utilized in radiation applications due to the nature of the charge storage mechanism and the thick tunneling oxides. Charge is stored in a conductive gate isolated from the silicon substrate by a tunnel oxide, typically thicker than 7 nm. This thick oxide accumulates 2-3 times more charge during radiation exposure than SONOS or nitride

Figure 1.1: The unique radiation requirements of space and military applications with regards to lifetime and single event doses. The area under the dotted line represents the capability of commercial off-the-shelf (COTS) electronics [2].

based (NROM<sup>TM</sup>) NVSM's. The radiated ions accumulating in the tunnel oxide create defects, which the charge in the conductive gate uses to escape the gate and the charge (memory state) is lost. In a SONOS structure, the charge must first escape the discrete trap it is stored in before tunneling to the trap and subsequently tunneling to the silicon bulk.

The Northrop Grumman Corporation has utilized SONOS NVSM's in a number of satellites and military applications such as the F-22 advanced fighter's electronically steered radar [1]. To this day, the SONOS technology is the only space-flown NVSM. SONOS devices are used to store module addressing and voltage biasing configurations for high-power Ga-As transistors in these applications [3].

| Voltage           | 7V            |  |  |

|-------------------|---------------|--|--|

| Current           | Low           |  |  |

| Speed             | < 10 ms       |  |  |

| Retention         | 10 Years      |  |  |

| Commercial        | 85 °C         |  |  |

| Military          | 125 °C        |  |  |

| Cycling           | 10⁴           |  |  |

| Radiation<br>Dose | 300 krad (Si) |  |  |

| Denisty           | 1 Mb          |  |  |

Table 1.2: Systems requirements for NVSM's utilized in space and military applications [4].

Typical NVSM's used in space and military applications must meet a number of specifications. Included are requirements for programming voltages and currents to ensure low power operation. Fast programming and read times are required given that

the longer it takes for a device to access and program, the more power it uses. NVSM's must retain data for 10-years within a range of specified temperatures. The device must be able to be programmed a number of times, but will generally not be repeatedly reprogrammed since it will be used as a data storage device. A lifetime radiation dose requirement and density of the memory array must be met in order to integrate the part into an electronic system.

Electronics operating in orbit of Earth no longer face radiation hazards solely from the natural environment, but also nuclear terrorism. The availability of nuclear materials due to the collapse of the Soviet Union in the late 1980's, coupled with the determination of hard-line regimes, such as North Korea, which has publicized its development of nuclear weapons and nuclear-capable long-range missiles [5], has made this threat increasingly relevant to NVMS system design.

Figure 1.2: Effect of a nuclear detonation on commercial and military satellites in Earth orbit [2].

Researchers have run computer simulations to examine the effects of a single 50 kT nuclear burst at a height of 120 km over the Earth. The radiation from the nuclear detonation immediately destroys all satellites and space systems within line-of-sight of the explosion. The radiation from the detonation is then collected by the Van Allen belts and trapped within the Earth's atmosphere. This trapped radiation will travel around the Earth in the Van Allen belts and destroy the remaining satellites which were shielded by the Earth from the initial blast. Computer simulations have determined that within 50 days (< 2 months), all of the remaining commercial and un-protected satellites will be destroyed by this trapped radiation [2].

Figure 1.3: Number of satellites remaining after simulated 50 kT nuclear detonation in the Earth's atmosphere [2].

Historically, the defense industry has been 2-4 generations behind commercial electronics corporations in semiconductor device scaling, Fig. 1.4. A good metric for device scaling is CMOS transistor gate length. Aggressive NVSM device scaling has not been a priority of the defense industry, since NVSM are mostly used in fighter jet

radars or satellite systems which require small volumes of non-volatile memory and have sufficient chip area for the required parts. However, the increasing complexity of electronic systems due to the integration of diverse microelectronics on a single chip (system-on-a-chip), have pushed scaling to new heights for both commercial and defense electronics. The benefits of SONOS transistors programmed with CHISEL/HHI mechanisms (speed, retention, power) could encourage increased government funding of the defense industry to scale its microelectronics and remain competitive with commercial semiconductor foundries.

Figure 1.4: Gate length dimension scaling of commercial and defense electronics industries over the past 25 years [6].

#### 1.2 NVSM Technologies for Space and Military Applications

Conventional non-volatile semiconductor memory (NVSM) devices store holes or electrons in a charge-storage layer in the gate dielectric. This charge can be stored in a variety of manners. The charge can either be stored in a conductive layer (floating gate) or in traps in the charge-storage layer (floating trap). NVSM devices are programmed by applying either a positive or negative voltage to the gate to promote the tunneling of electrons or holes, respectively, into the charge-storage medium.

Figure 1.5: Unique temperature and radiation requirements for inter-planetary exploration [7].

In order to qualify an NVSM for space and military applications, we must examine the specific characteristics of that technology. Several key electrical characteristics of EEPROM devices include retention, endurance, and programming

speed. Retention refers to the ability of the device to store and sense charge in the nitride layer after a number of write and erase cycles at a specific temperature. Endurance refers to the ability of a device to withstand repeated write and erase cycles and still be able to retain and recover charge. Programming speed refers to the time over which the programming voltage is applied to the gate in order to switch the device from the write to the erase state.

#### 1.2.1 Floating Gate

Floating gate transistors are written using channel hot electron (CHE) injection and erased using Fowler-Norheim (FN) tunneling. To program the device with CHE, a high lateral electric field is applied along the channel of the device, causing electrons to accelerate through the channel until they are scattered by the lattice or another carrier. The appropriate vertical field will result in "lucky" electrons, which will accumulate enough energy to cross the Si-SiO<sub>2</sub> barrier and inject themselves into the gate dielectric where they are stored in traps. The Carrier Hot Electron (CHE) current is defined using the equation [8]

$$I_{G} = \left(\frac{\Delta L}{\lambda_{R}}\right) \left(\frac{\lambda_{S} \varepsilon_{y}}{4\phi_{B}}\right) I_{S} e^{-\frac{\phi B}{\lambda_{S} \varepsilon_{y}}} e^{-\frac{X_{B}}{\lambda_{OX}}} e^{-\frac{\bar{\chi}}{\lambda_{S}}}$$

$$(1.1)$$

where  $\Delta L$  is the length of the charge injection region,  $\lambda_R$  is the redirection mean free path,  $\lambda_{OX}$  is the mean free path in silicon-dioxide,  $\lambda_S$  is the electron mean free path in silicon,  $\phi_B$  is the SiO<sub>2</sub> barrier height measured from the substrate,  $I_S$  is the source

current,  $E_y$  is the maximum vertical field in the vicinity of the drain, expressed as  $E_y = \frac{qN_AX_d}{\varepsilon_S}$  where  $N_A$  is the substrate doping,  $X_D$  is the drain depletion width, and  $\varepsilon_S$  is the permittivity of silicon.

Floating gate devices offer rapid programming using channel hot electron injection and high density, since two devices may share a single source line [9]. Floating gate transistors are currently the most widely used NVSM devices for applications such as memory cards used in digital cameras and cellular phones, smart cards, and automotive applications. These applications all require low voltage and low power operation, rapid programming, extreme high and low temperature tolerance, long-term data retention, and endurance up to one-million write/erase cycles [7].

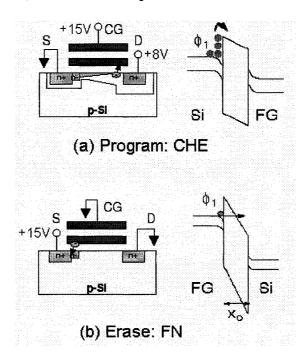

Figure 1.6: Write/erase mechanisms of mainstream flash technologies. Programming voltages and energy-band diagrams for a) CHE injection write and b) FN erase operation [10].

The conductive charge storage medium in a floating gate Flash memory transistor allows a single defect in the oxide to remove all of the stored charge. The charge will tunnel from the conductive gate to the interface defect then to the silicon substrate. Due to this vulnerability to single-defect charge loss, floating gate devices suffer from reliability issues stemming from oxide hot carrier degradation, punch-through avalanche effects, and tunnel oxide scaling limits [11, 12]. Floating gate devices also suffer from higher programming voltages and cell scaling limits [13].

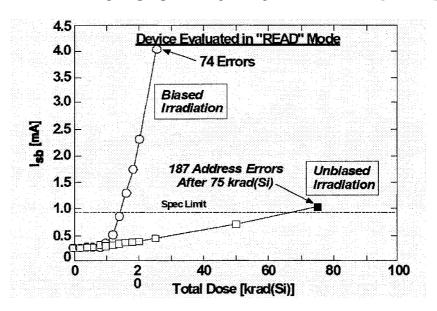

Figure 1.7: Experimental data showing floating gate failure, depicted as an increase in leakage current versus total dose radiation [14].

Floating gate memory, the traditional choice for many memory-intensive applications, has several major limitations with respect to cell size scaling and programming voltage [15]. Due to the complicated nature of the gate dielectric, scaling the device below the 100 nm node is difficult. Recent advances show the ability of the device to be scaled below the 120 nm node [16]. However, the complex capacitances

involved in the gate dielectric hamper vertical gate scaling, requiring higher programming voltages. Floating gate memories also suffer from dielectric hot carrier degradation which damages the bottom insulating oxide during the write function, avalanche effects at the drain junction, and high-voltage breakdown of the oxides due to the high electric fields required to program these devices [13]. However, the major drawback of the floating gate technology is its inability to function in a radiation environment, with peripheral charge pumping circuits failing at 10krad, sensing amplifiers failing at 50krad, and floating gate NVSM erasure at 100krad [14]. This performance is eclipsed by the SONOS technology which can operate without incident at radiation levels up to 500krad [1].

#### **1.2.2 SONOS**

Floating trap devices, such as polysilicon-oxide-nitride-oxide-silicon (SONOS), transistors offer several advantages over floating gate transistors. SONOS devices store charge in spatially isolated deep level traps in the charge-storage layer, see Fig. 1.8. The SONOS device is written by grounding the source, drain, and bulk, and applying a positive voltage to the gate, enabling Fowler-Nordheim tunneling of electrons to the charge-storage medium where they are stored in traps [17]. Erasing the SONOS device is accomplished by grounding the source, drain, and bulk, and applying a negative voltage to the gate, causing holes to tunnel from the silicon substrate and trap in the nitride layer [13]. The charge remains trapped in the nitride after all voltages are removed.

Figure 1.8: The vertical cross-section of a SONOS device, X's represent charge storage traps in the silicon nitride film.

Storing charge in traps in the nitride layer prevents charge from tunneling through the oxide layers to either the gate or the substrate when the transistor is in the retention mode. Eventually, holes and electrons will escape from their traps and tunnel back to the silicon bulk. This occurs over an extremely long period of time, typically, 10 to 100 years. There are several mechanisms responsible for charge loss: trap to band tunneling, trap to trap tunneling, and thermal excitation of electrons [18]. In an N-channel SONOS device, storing negative charge, electrons, in the nitride will cause the threshold voltage to increase, and storing positive charge, holes, in the nitride will cause the threshold voltage to decrease.

SONOS devices offer several advantages over floating gate memory transistors. SONOS devices have a higher tolerance to radiation [19], use lower operating voltages and less current, have greater endurance to extended write/erase cycling, and are compatible with scaled 'standard' CMOS technology with fewer processing steps [15]. SONOS transistors are more easily scaled than floating gate memory devices. The

|                                    | SONOS                                                     | Floating Gate                                                           |

|------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|

| Carriers                           | Write: Electrons<br>Erase: Holes                          | Electrons                                                               |

| Structure                          | One Gate Two Gates One Dielectric Two Dielectric          |                                                                         |

| Gate Control                       | Direct Capacitively coupl control gate                    |                                                                         |

| Scaleable                          | Linear with program voltage                               | Not easily scaled                                                       |

| Reliability                        | Immune to single defect memory loss                       | Susceptible to single defect memory loss in tunneling oxide             |

| Programming Voltages               | Lower voltages (5-7 V)                                    | High Voltages (~15 V)                                                   |

| Electric Fields in Tunnel<br>Oxide | Reduced Fields (Modified<br>Fowler Nordheim<br>Tunneling) | High Fields (Fowler<br>Nordheim Tunneling and<br>Channel Hot Electrons) |

Table 1.3: Summary of the major differences between SONOS and floating gate technologies [20].

nature of the floating gate makes it difficult to discern the exact voltage and field applied to the conductive gate. Bias is not directly applied to the gate, which is surrounded by four oxide and nitride films. A SONOS device is biased by applying a voltage directly to the gate, making it is easier to scale the programming voltages with the gate dielectric thickness [21].

#### 1.2.3 **NROM**<sup>TM</sup>

Several novel methods for programming SONOS devices can be utilized to provide performance enhancements over the floating gate technology. One such innovation is the concept of storing charge in two distinct localized regions in the

Figure 1.9: Programming a short-channel NROM<sup>TM</sup> transistor using channel hot electron (CHE) and hot hole injection (HHI) at the drain side of the device [22].

nitride [23]. B. Eitan, et al., pioneered the research and development of the so-called 2-Bit NROM<sup>TM</sup>. This device utilizes channel hot electron (CHE) injection at the source and drain junctions to store a small amount of charge locally in the nitride. A positive voltage is applied to the gate, a separate positive voltage is applied to either the source or the drain to select that side of the gate dielectric for charge injection, and the remaining terminals are grounded [24]. The tunneling oxide for NROM<sup>TM</sup> devices must be at least 3 nm thick in order to significantly block direct tunneling during the write and erase operations [23] and reduce so-called 'back-tunneling' in order to enhance the charge storage or memory retention.

Erasure of the NROM<sup>TM</sup> device is accomplished using hot hole injection (HHI).

A negative voltage is applied to the gate, a positive voltage is applied to either the

source or drain, selecting the side of the transistor where the holes will be injected, and the remaining terminals are grounded [24]. The blocking oxide must be thick enough (> 4 nm) in order to prevent electron injection from the gate during the erase operation. The device is read by performing a "reverse read" operation where the transistor is read in the direction opposite the write or erase [25]. For example, to read the bit at the drain side, a small voltage of roughly 1.5 volts will be applied to the source, the drain and bulk will be grounded, and the gate will be swept from 0 to 3 volts [24]. The exact

#### **NROM Double Storage Density**

Figure 1.10: Multi-bit data storage in a single NROM<sup>TM</sup> transistor achieved via independently injecting charge at both the source and drain junctions [22].

'read' voltage will depend on the device design, since too low a voltage will not provide sufficient drive current and too high a voltage will cause excessive drain induced barrier lowering, thereby degrading the programming window. The programming and read operations are detailed in Table 1.4.

The NROM<sup>TM</sup> device is a hybrid of the floating gate and floating trap devices. It possesses the quick programming time and source sharing of the floating gate technology along with the retention endurance, durability, and low operating power and voltages of the SONOS technology. Research has shown NROM<sup>TM</sup> devices can be easily scaled with CMOS technology, possess short write (10μs) and erase times (10ms) [26], use low programming voltages (5-7 V), share source lines to achieve cell sizes of 2.5- 5F<sup>2</sup>, exhibits write/erase durability (up to 10<sup>5</sup> cycles), and long term retention (>10

|         | Bit 1  |         |         | Bit 2  |         |         |

|---------|--------|---------|---------|--------|---------|---------|

| -       | WL (V) | BL1 (V) | BL2 (V) | WL (V) | BL1 (V) | BL2 (V) |

| Write   | 7      | 4       | 0       | 7      | 0       | 4       |

| Erase   | -7     | 4       | 0       | -7     | 0       | 4       |

| Reverse | 0-3    | 0       | 1.5     | 0-3    | 1.5     | 0       |

| Read    |        |         |         |        |         |         |

Table 1.4: Applied voltages for the write, erase, and read states for NROM™ 2-bit transistor operation with 90Å equivalent oxide gate thickness. Applied voltages are for the Word Line (WL), Bit Line 1 (BL1), and Bit Line 2 (BL2). The substrate remains grounded in all states. Voltages are for a device with a 36Å tunnel oxide, 30Å siliconrich nitride, and a 36Å blocking oxide. All terminals are grounded for a device in the idle/retention mode.

years) due to the increased tunnel oxide thickness as compared to their SONOS counterparts [24]. This concept has been demonstrated on NSONOS transistors with gate lengths as small as  $0.13~\mu m$  [27].

Reliability issues involving damage to the gate dielectric and residual charge buildup in the charge-storage layer, due to mismatch of the hole and electron injection areas, have led researchers to develop new methods for programming and erasing 2-bit NVSM's. The first alternative method uses hot electron injection to write a device and uniform tunneling to erase the device [26]. Hot electron injection provides fast write times and storage of electrons in two distinct, localized areas. However, residual charge buildup occurs over time due to small lateral differences along the channel of the location of electrons injected during the write operation and the location of holes injected during device erasure. This residual charge causes the threshold voltage window to degrade after as few as 100 write/erase cycles [28].

A uniform channel erase can also be used to cycle the NROM<sup>TM</sup> structure. During a channel erase, holes tunnel from the entire length of the silicon substrate, ensuring that the nitride is completely erased [26]. Using a uniform channel erase will erase both data bits, limiting the flexibility of this device, but allowing for Flash operation. The drawbacks to uniform channel erasure include increased erase gate voltage and a reduced tunnel oxide thickness to achieve hole tunneling.

Another alternative programming method utilizes hot hole injection to *write* and Fowler-Nordheim tunneling of electrons to *erase* the device [29]. Typically programming the device with electrons is referred to as *writing* the device and programming with holes is referred to as *erasing* the device. However, C.C. Yeh, et al, use the opposite convention. Their arrangement uses hot hole injection for fast programming times and 2-bit memory operation. These researchers contend Fowler-Nordheim (FN) tunneled electrons occupy traps deep in the nitride and electrons in shallow traps will be drawn out by the high electric fields. Programming with channel

Figure: 1.11 Write/erase endurance with CHE/tunneling and CHE/HHI in an NROM<sup>TM</sup> VNSM. Hot hole injection results in electron build up over the channel [26].

hot electron (CHE) injection randomly captures the electrons in deep and shallow traps. The electrons in shallow traps will easily escape during charge retention [29]. However, hot hole injection causes greater damage to the gate dielectric during programming than channel hot electron injection, resulting in degraded retention performance after write/erase cycling [26]. These varied programming systems represent the versatility of the NROM<sup>TM</sup> device and its suitability for use in space and military applications.

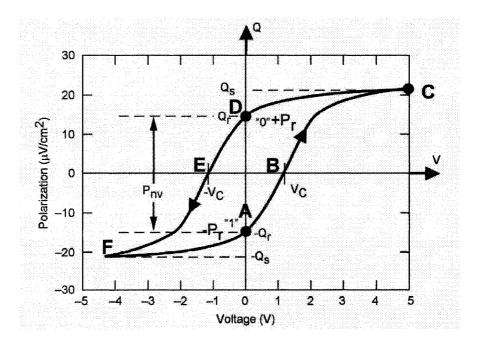

#### 1.2.3 Novel Concept NVSM's

In addition to storing charge in a film in the gate dielectric of a transistor, there are several competitors to the SONOS technology for use in space and military

applications. These technologies utilize the change in polarity, magnetic direction, or physical composition of a film in the gate dielectric of a transistor. Ferroelectric memory (FRAM) uses a ferroelectric material PbZr<sub>X</sub>Ti<sub>1-X</sub>O<sub>3</sub> (PZT) or SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> (SBT) film. Applying a positive electric field to the film causes the polarization of the film to shift positively. Conversely, a negative voltage will cause a negative shift in polarization [30].

These films are used in capacitors as replacements for the oxide gate dielectric. The polarity of these films can be read by applying a voltage to the gate and sensing a high (logic 1) and low (logic 0) read current [31]. This technology features extremely fast read (55 ns) and write (100ns) times, high endurance (10<sup>8</sup>-10<sup>13</sup> write/erase cycles) and 10-year retention at 150C [32-34]. However, FeRAM devices require a large amount of chip area and are not compatible with standard CMOS processing [33].

Figure 1.12: Hysteresis loop of a ferroelectric capacitor [35].

Another novel NVSM is magnetic memory (MRAM). This technology utilizes a ferromagnetic film which can switch magnetic direction via an applied electric field. Pairing this film with another ferromagnetic film with a fixed magnetic direction in a gate stack of a transistor or capacitor can create a magnetic memory device. If the magnetic orientations of the free and fixed films are in the same direction, the junction will have a low resistance. A high resistance will be obtained if the magnetic orientations are opposite [36, 37]. Applying a read voltage will produce a high read current if the resistance is low and a low read current for a high resistance, effectively reading out the memory sate [38].

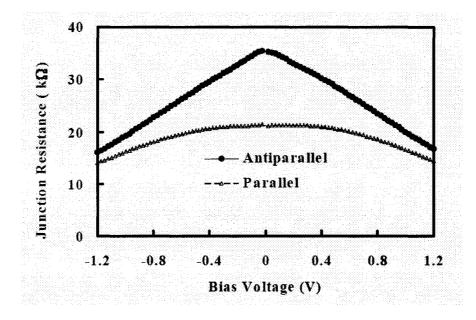

Figure 1.13: Bias voltage dependence of the anti-parallel and parallel resistances for a magnetic tunneling junction [39].

The MRAM technology features extremely low programming voltages (1-3.3V), nanosecond read and programming times, 10 year data retention, infinite cycling, and high density. However, this technology is plagued by high currents required to switch

the magnetic orientation of the free film, thermal relaxation where the film spontaneously switches its magnetic orientation, and incompatibility with standard CMOS processing [40]. In addition, process control has been a major obstacle to manufacturing cost-effective MRAM devices.

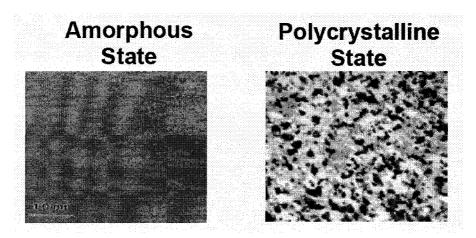

Finally, the phase change memory (PRAM) alters the physical state of a film in the gate dielectric. PRAM uses 'Chalcogenide' films which are composed of group VI elements, such as GeSbTe (GST) alloys. The application of heat changes the film from an amorphous state, characterized by a dull appearance and high electrical resistance

Figure 1.14: Transmission Electron Microscope images of the two phases of a GeSbTe alloy [41].

(mega-ohms), to a polycrystalline state, characterized by a highly reflective appearance and low electrical resistance (kilo-ohms) [41]. This technology is currently in use in CD/DVD-RW media where difference in reflectivity between the two states is used to determine the memory state.

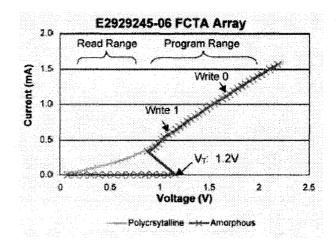

PRAM memory devices use a Chalcogenide film in the gate of a transistor or capacitor. The Chalcogenide film is locally heated and, depending on the heating time,

becomes either amorphous or crystalline, altering the resistance of the junction [42]. The memory state is sensed by applying a read voltage and measuring the resulting current. This technology features nanosecond programming times, greater than 10 year retention,  $10^{12}$  programming cycles with low current, high density, moderate scaling, and radiation hardness up to 2Mrad [40, 43, 44]. However, PRAM films often become frozen in a specific state when high current is applied, thermal cross-talk heats neighboring bits during programming, and high programming currents (mA) are required [45, 46].

Figure 1.15: Memory effect of a PRAM [46].

### 1.3 Scope of the Dissertation

Nonvolatile semiconductor memory devices operating off of fixed battery supplies in space and military applications require low-power programming and long-term data retention. The memory device must not draw more than a milliamp of current. Scaling programming voltages to below 5V aids in reducing the power dissipated by the

device. However, rapid programming of a memory is useless if the device cannot retain the data for up to 10 years without a power supply. These two requirements are central to the design of a radiation-hardened memory device suitable for space and military applications. This dissertation focuses on scaling the programming voltages and times through utilizing a write mechanism adapted from the floating gate technology and developing a method to forecast 10-year retention of a SONOS memory transistor. This includes characterizing the write and erase processes of scaled SNROM devices using channel initiated secondary electron (CHISEL) injection, NROM™ programmed with channel hot electron (CHE) injection, characterizing damage to the interface of the silicon bulk and silicon-dioxide layers in various NVSM devices, and measuring and extrapolating data retention of SONOS devices at elevated temperatures.

A low power substrate injection nitride based (SNROM) device is presented, for the first time, and programming using channel initiated secondary electron (CHISEL) injection is analyzed and modeled in Chapter 2. The SNROM device is a short-channel transistor with an oxide-nitride-oxide charge storage gate dielectric. The CHISEL concept is demonstrated by programming SNROM devices with a negative bulk bias and positive drain and gate biases and measuring the obtained memory window. The threshold voltage of the transistor is modeled and extracted from the measured channel current during CHISEL programming. Impact ionization current at the drain side of the device is measured and correlated to the injected current and threshold voltage shift in the SNROM device.

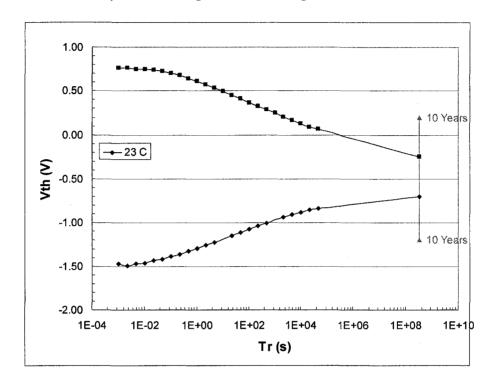

Chapter 3 presents retention measurements performed on SONOS devices at

temperatures ranging from room to 250°C. Retention models based on the density of traps in the nitride are employed to model the decay rate of the threshold voltage for a specific temperature and time. Data retention is characterized using charge decay rate modeling. Scaled SONOS transistor fabrication techniques and design concerns are outlined in Chapter 4. Techniques for fabricating sub-micron SONOS transistors using a source-drain drive-in anneal to create a 0.5 μm channel length are presented and simulated.

Chapter 5 concerns the electrical characterization of SONOS devices. Oxide degradation during charge injection is studied using charge pumping measurements. Charge pumping is performed with both square and triangular voltage pulses and the two methods are compared and contrasted. Linear voltage ramp, capacitance, and variable frequency charge pumping measurements are utilized to characterize SONOS gate dielectrics. Chapter 6 presents results of electrical measurements, performed in the course of this research, on SONOS, NROM™, and SNROM devices for qualification for space and military applications. Conventional NVSM devices are programmed at different voltages, interface quality and initial memory window are measured up to 10<sup>6</sup> write/erase cycles, and data retention is measured at temperatures up to 250°C. Threshold voltage decay trends are studied and a standard procedure for forecasting 10-year charge retention is formed. Chapter 7 presents conclusions based on the analysis, measurement, and modeling of NVSM devices in this dissertation. Recommendations for future research are presented.

# Chapter 2

# **Channel Initiated Secondary Electron Injection (CHISEL) Programming in SNROM Transistors**

Programming SONOS devices for space and military applications requires low currents, rapid charge transport, and minimal power dissipation. Conventional programming methods such as Modified Fowler-Nordheim (MFN) and direct tunneling (DT) have been introduced in Chapter 1. Tunneling mechanisms require very little current but necessitate relatively high programming voltages, which have reached the scaling limit. The gate voltage determines the electric field in the gate stack and the speed of the programming operation. SONOS transistors fabricated with conventional SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> films cannot be further vertically scaled due to the thickness requirements of the oxides, necessary for insulating during the retention mode, and the nitride, requiring a certain dimension in order to have enough traps to store a sufficiently large volume of charge. In addition, programming using tunneling requires several milliseconds to obtain an adequate memory window.

### 2.1 CHISEL Injection in Floating Gate Transistors

Floating gate devices are programmed by applying high vertical and lateral electric fields in order to impart enough energy to excite electrons flowing in the channel over the bottom oxide barrier. Channel hot electron injection has recently been

adapted for use in SONOS transistors, with the pseudonym NROM™, meaning nitride based read only memory [23]. The NROM™ structure is a short-channel SONOS device which is programmed using hot electron and hot hole injection. Recently, researchers working on floating gate devices have begun pioneering a newer programming mechanism known as CHannel Initiated Secondary ELectron (CHISEL) injection [47]. This programming mechanism is not only more efficient and faster than CHE injection, but it requires smaller channel currents and programming voltages [48]. Programming with CHISEL injection has not been widely studied in published literature for use in SONOS NVSM's for use in space and military applications.

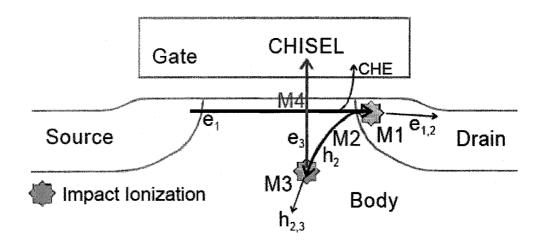

Figure 2.1: Programming a floating gate transistor with CHISEL injection. Impact ionizations create hole currents  $(h_{2,3})$  and electron currents  $(e_{2,3})$  [49].

CHISEL programming of a floating gate transistor is similar to channel hot electron injection, outlined in Chapter 1. Positive biases are applied to the gate and the drain junctions and a negative bias is applied to the substrate. The drain voltage is typically equal to or greater than the gate voltage. An inversion layer is formed in the channel due to the gate voltage, and pinches off towards the drain junction. Electrons

flow in the channel from the source to the drain (e<sub>1</sub>). A small portion of the electrons gain enough energy to become 'hot' (CHE) and inject into the gate dielectric due to the high lateral electric field in the channel. At the drain junction, it is believed that the electrons traveling through the channel undergo an impact ionization at the region of the inversion layer pinch-off [49, 50].

This impact ionization creates an electron-hole pair (e<sub>2</sub>, h<sub>2</sub>), where the electron (e<sub>2</sub>) is either accelerated to the drain or into the channel to propagate further impact ionizations. The hole (h<sub>2</sub>) is accelerated towards the substrate due to the negative bulk bias, where the hole may trigger a secondary impact ionization, creating another electron-hole pair (e<sub>3</sub>, h<sub>3</sub>). The hole (h<sub>3</sub>) is accelerated to the bulk by the vertical electric field and a portion of the ionized electrons (e<sub>3</sub>) are accelerated into the channel and injected into the gate dielectric [49].

Figure 2.2: Floating gate memory programmed with CHISEL and CHE injection. CHISEL injection is one decade faster than CHE injection [51].

Therefore, the drain current may be expressed as a combination of the channel current  $(e_S)$  and electron currents from the primary  $(e_1)$  and secondary  $(e_2)$  impact ionizations.

There are several advantages to programming a floating gate transistor with CHISEL versus programming with CHE [52]:

- 1) Programming times are one decade faster

- 2) Programming voltages are comparable or smaller

- 3) Channel current required for charge injection is smaller

- 4) Damage to oxide films in gate dielectric is comparable or less

The current injected into the gate of a floating gate transistor has been extensively modeled and may be expressed as a function of the drain and bulk currents

$$\frac{I_G}{I_D} = C(E_{ox}) \cdot \left(\frac{I_B}{I_D}\right)^{\alpha} \tag{2.1}$$

where  $\alpha = \Phi_B/\Phi_{II} \approx 2.5$ , where  $\Phi_B$  is the Si-SiO<sub>2</sub> oxide barrier height and  $\Phi_{II}$  is the effective threshold for impact ionization [47].

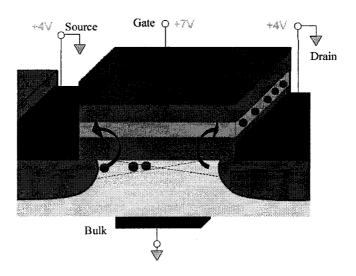

### 2.2 CHISEL Injection in SNROM Transistors

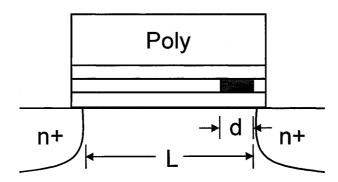

This dissertation presents unique research on a novel short-channel (10 x 0.22µm) NVSM device programmed with CHISEL injection. The gate dielectric is composed of a 36Å tunnel oxide, a 30Å oxygen-rich oxynitride, and a 36Å blocking oxide. These devices will be referred to as substrate injection nitride based (SNROM)

devices. The tunneling oxides of these devices are thicker than tunneling oxides in conventional SONOS transistors, which are typically 15 to 20 Å thick. The relative dielectric constant for the oxynitride film is 5.07, with an equivalent oxide thickness of 23.5Å. These transistors are intended to be programmed with a channel hot electron (CHE) write and a hot hole injection (HHI) erase. It should be noted that these transistors are not optimized for CHISEL injection. Future SNROM structures, film thickness, and ion implants can be optimized for CHISEL programming in order to provide enhanced results.

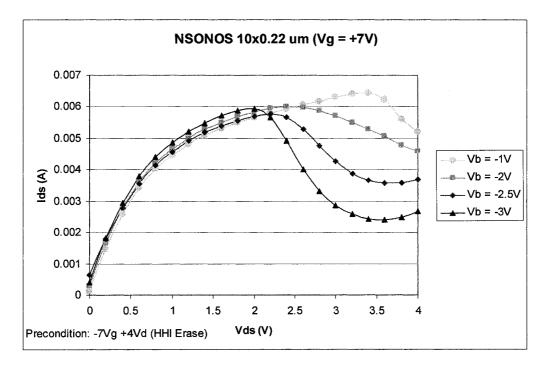

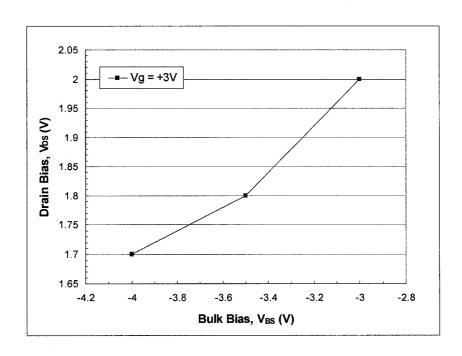

Modeling short-channel SNROM transistors programming with CHISEL and CHE injection begins with demonstrating memory operation. SNROM devices (10 x 0.22  $\mu$ m) were written with CHISEL injection by applying +3V to the gate, +2.5V to

Figure 2.3: Vertical cross-section of a short-channel SNROM transistor during CHISEL injection. The drain current is composed of electron currents ( $e_{S,1,2}$ ).

the drain, -4V to the substrate, and grounding the source. These transistors were erased using HHI by applying -7V to the gate, +4V to the drain, and grounding the source and substrate. The programming times for both write and erase were 5 ms, each. SNROM devices programmed under these conditions produced a 2 - 2.7 volt memory window. Programming, read, and retention voltages and timing were controlled using the NVSM characterization setup described in section 5.2.

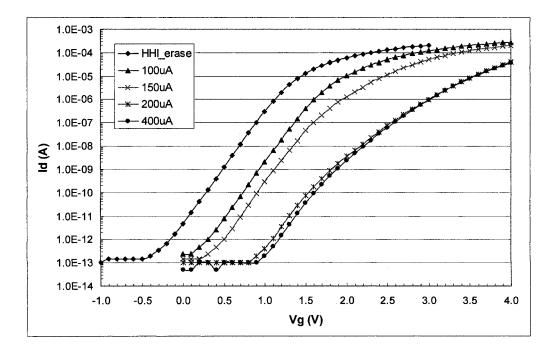

Figure 2.4: Drain current versus gate voltage measurements depicting SNROM programming with CHISEL injection at various gate and substrate biases. Drain bias during I-V sweeps is 50mV. The device is preconditioned with a hot hole injection (HHI) erase at the drain (red). The device is programmed with 2-3V applied to the gate, -3 to -4V applied to the substrate, and a drain bias of +3.5V (blue curves).

CHISEL programming of an SNROM transistor occurs in the same manner as CHISEL injection in a floating gate transistor, described in section 2.1, with the exception of the electron current from the secondary impact ionization. Electrical

characterization, discussed later in this section, has shown the drain current is approximately equal to the channel current (e<sub>S</sub>) and electron currents from the primary (e<sub>1</sub>) and secondary (e<sub>2</sub>) impact ionizations. Therefore, we model the electron current from the secondary impact ionization as e<sub>2-CHISEL</sub>, which is the portion of the ionized electrons which are injected into the nitride, and e<sub>2</sub>, which is the remainder of the electrons which are captured by the drain.

Figure 2.5: Threshold voltage versus programming time for a short-channel 10 x 0.21  $\mu$ m SNROM transistor programming with CHISEL and HHI mechanisms. CHISEL write is performed by applying +3V to the gate, +3.5V to the drain, -4V to the substrate, and grounding the source for 5ms. HHI erase is performed by applying -7V to the gate, +4V to the drain, and grounding the source and substrate for 5ms.

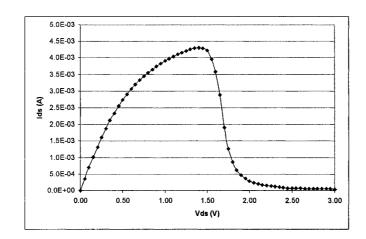

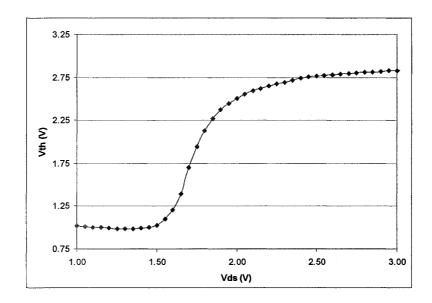

The threshold voltage of the transistor may be modeled from the drain to source current of an SNROM transistor programmed with CHISEL injection, giving insight into the current-multiplication and impact ionization occurring within the channel and substrate of the device. The SNROM device is programmed using an HP4145 parameter analyzer. The gate voltage is fixed at +3 V, -4 V is applied to the substrate, and the source is grounded. The channel current, measured at the drain, is monitored as the drain voltage is swept from zero to +3.5 V. The measurement is more accurate when the source current is measured, since this current does not include the electrons escaping to the drain from the electron-hole pairs generated by impact ionizations, a critical component for CHISEL injection. As the drain voltage is swept, the channel current increases, as is expected for a conventional MOS transistor. However, when the lateral electric fields, created by the drain bias, are high enough, impact ionizations begin to occur at the drain junction and in the bulk, and CHISEL injection occurs.

### 2.2.1 Modeling SNROM Threshold Voltage Shift during CHISEL Injection

During CHISEL injection, electrons are excited over the silicon-dioxide barrier and trap in the nitride, creating a positive shift in the threshold voltage, where the threshold voltage is expressed as [21]

$$V_{th} = \Phi_{GS} + 2\Phi_F + \frac{\sqrt{4\varepsilon_{st}qN_B\Phi_F}}{C_{eff}} - Q_N \left[ \frac{x_{OB}}{\varepsilon_{OX}} + \frac{x_n}{2\varepsilon_n} \right] - \frac{Q_{SS} + Q_{it}}{C_{eff}}$$

(2.2)

where  $\Phi_{GS}$  is the gate to semiconductor work function,  $\Phi_F$  is the Fermi potential,  $\epsilon_{SI}$  is the permittivity of the silicon substrate, q is the charge of an electron,  $N_B$  is the channel doping density,  $C_{eff}$  is the effective capacitance,  $Q_N$  is the charge trapped in the nitride,  $Q_{SS}$  is the charge at the Si-SiO<sub>2</sub> interface, and  $Q_{it}$  is the charge stored in interface traps

Figure 2.6: Drain current of an SNROM transistor (W/L =  $10 \times 0.22 \mu m$ ) measured during CHISEL programming with 3V applied to the gate and -4V applied to the bulk. in the bottom oxide [21].

The threshold voltage increases until it approaches the value of the fixed gate voltage, causing the channel to turn off, evident in the decrease in channel current, see Fig. 2.6. This effect allows us to extract and monitor the change in the threshold voltage of the device as the drain voltage is swept. The channel current may be expressed as

$$I_{DS} = \frac{1}{2} \beta_0 (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(2.3)

where  $V_{GS}$  is the gate voltage,  $V_{TH}$  is the threshold voltage,  $V_{DS}$  is the drain bias,  $\lambda$  is the inverse of the Early voltage, and  $\beta_0 = \mu_n C_{OX} W/L$  where  $\mu_n$  is the effective mobility for holes, and W and L are the width and length of the transistor, respectively. Solving Eq. 2.3 for the threshold voltage yields

$$V_{TH} = V_{GS} - \sqrt{\frac{2I_{DS}}{(1 + \lambda V_{DS})\beta_0}}$$

(2.4)

The extracted SNROM threshold voltage shows the CHISEL injection occurs when the lateral electric field is high enough to create hot carriers and the subsequent impact ionizations. The current from the impact ionizations is measured during the CHISEL injection. This current is the sum of the electrons which are not injected from the channel current, primary impact ionization, and electrons not injected following the secondary impact ionization.

Figure 2.7: Extrapolated threshold voltage shift of the SNROM transistor during CHISEL programming.

The charge per unit area injected and trapped in the nitride may be calculated from the threshold voltage shift. The threshold voltage shift as a function of injected charge may be expressed as

$$\Delta V_{TH} = \Delta Q_N' \left( \frac{X_{OB}}{\varepsilon_{OX}} + \frac{X_N}{2\varepsilon_N} \right) \tag{2.5}$$

where  $Q_N$  is the charge density in the nitride,  $X_{OB}$ ,  $\epsilon_{OX}$ ,  $X_N$ , and  $\epsilon_N$  are the thickness and permittivity of the blocking oxide and nitride layers, respectively. Since the charge is not injected over the entire channel length, the charge density is expressed as  $Q'_N = Q_N \left(\frac{d}{L}\right)$  where L is the channel length and d is the length of the region where the charge is injected. This scaling factor represents the equivalent effect on the threshold voltage of a smaller volume of charge injected over a localized region of the channel. The charge is then calculated by multiplying the charge density by the area of the SNROM device.

Figure 2.8: Lateral cross-section of a SNROM transistor depicting the CHISEL charge injection region (red).

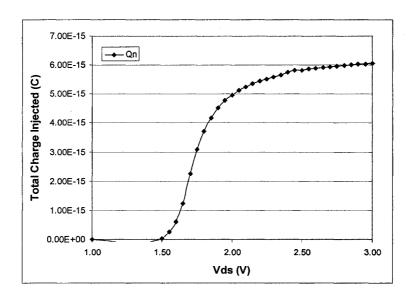

The threshold voltage shift has been calculated previously from the channel current during programming. The change in the threshold voltage is used to numerically compute the amount of charge injected into the nitride, Fig. 2.9. The current injected into the nitride may be expressed as change in charge per unit time

$$I_{inj} = \frac{dQ_N}{dt} = \frac{dQ_N}{dV_{DS}} \cdot \frac{dV_{DS}}{dt}$$

(2.6)

Figure 2.9: Trapped charge required to produce observed V<sub>TH</sub> shift.

During the SNROM CHISEL injection measurement, the drain voltage is swept from 0 to 3.5 volts in steps of 0.1V. The drain voltage step function is approximated as a ramped voltage with a slope expressed as alpha,  $\alpha = \frac{dV_{DS}}{dt}$ . The ramp rate (slope) used for CHISEL injection was 500 mV/second. Substituting the ramp rate into Eq. 2.6, we may express the injected current as

$$I_{inj} = \alpha \frac{dQ_N}{dV_{DS}} \tag{2.7}$$

The change in the threshold voltage, extrapolated from the channel current during charge injection, is substituted into Eq. 2.5 to calculate the total charge injected. The channel length is  $0.22~\mu m$  and the length of the charge injection region is approximate from literature as 450 Å [53]. The slope of the charge with respect to the

Figure 2.10: Drain voltage stepped (solid) during SNROM CHISEL programming approximated as a ramped voltage (dashed).

drain voltage is substituted into Eq. 2.7, with the ramp rate (500 mV/second), to calculate the current trapping in the nitride which will shift the threshold voltage as measured. We will refer to this required injection current as the 'calculated injection current'. The total injected charge,  $5.83 \times 10^{-15}$  C, may be divided by the charge per electron,  $1.6 \times 10^{-19}$  C/e<sup>-</sup>, to calculate that 36,000 electrons are injected into the nitride

Figure 2.11: Current injected into the gate dielectric and trapped in the nitride extrapolated from the threshold voltage shift.

during the CHISEL programming. In addition, the total current injected into the nitride, 58 fA, is very low. These results demonstrate the low-power operation of the SNROM.

### 2.2.2 SNROM CHISEL Impact Ionization Current

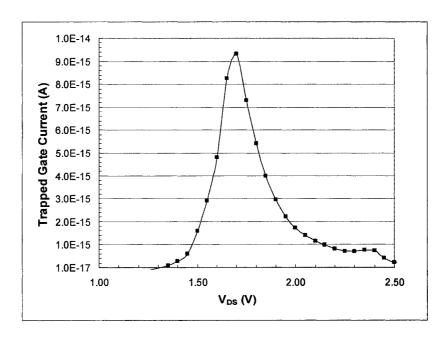

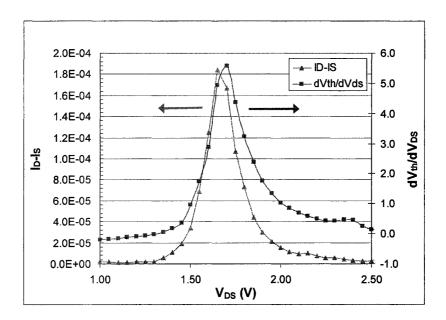

The calculated current injected into the nitride may be correlated to the ionization current measured at the drain terminal. The ionization current, may be expressed as the difference between the source and drain currents during DC

Figure 2.12: Measured impact ionization current (triangles) and slope of threshold voltage shift (squares) during SNROM CHISEL injection.

programming of the SNROM, since the majority of the electrons from the impact ionizations are not injected but are captured by the drain terminal.

$$I_{lon} = \left| I_D \right| - \left| I_S \right| \tag{2.8}$$

Plotting the measured impact ionization current versus the change in the threshold

voltage with respect to drain voltage, we see that the impact ionization current spikes when the threshold voltage changes, Fig. 2.12. The threshold voltage of the SNROM transistor is shifted when the electrons generated by the impact ionizations are injected into the nitride.

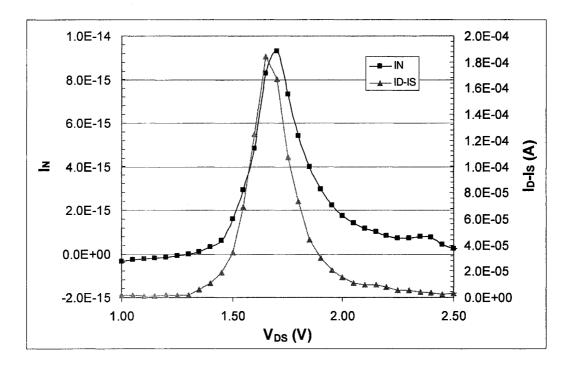

Figure 2.13: Calculated trapped injection current (dark squares) and measured impact ionization current (light triangles) in the SNROM device.

As already discussed, the electron current from the impact ionizations is proportional to the current injected into the nitride. This relationship is demonstrated by plotting the calculated injection current with the measured impact ionization current while the drain bias is varied, Fig. 2.13. Both currents peak at a drain bias of 1.7V, where the CHISEL injection and threshold voltage change occur. This provides a visual correlation between the ionization current, the current injected and trapped in the nitride, and the shift in the threshold voltage.

# Chapter 3

# Modeling Density of Traps in Oxynitride Charge Storage Films in Scaled SONOS Transistors

In order to achieve improved SONOS charge retention, oxygen-rich silicon nitride films called oxynitrides (SiO<sub>x</sub>N<sub>y</sub>) have been used in the fabrication of the devices tested in this dissertation. Kapoor et al investigated oxynitrides as storage media, replacing silicon-rich nitride layers. Oxynitride films have lower trap densities compared to silicon-rich nitrides [54], which is verified in this dissertation. Oxynitride films demonstrate reduced Coulombic repulsion between trapped charges. Coulombic repulsion contributes to these charges coming free from their bonds and creating interface traps, which are used as stepping-stones for charge stored in the nitride to escape to the silicon substrate.

A decrease in the interface trap density has been correlated with an increase in oxygen content in the oxynitride film [54]. Thin oxynitride films provide an improved gate dielectric compared to silicon nitride films. The addition of oxygen impurities in the oxynitride reduces the trap densities by compensating the silicon-dangling bonds at the oxide-oxynitride interface and results in a decreased charge decay rate and current conduction and improves the SONOS memory properties [55]. Interface states must be minimized in SONOS memory devices to achieve superior device performance, such as lower programming voltages, and shorter write and erase times [56].

### 3.1 Historical Perspective

Since the invention of the nitride based memory structure in 1967 [57], there has been a great deal of experimental and analytical work focusing on understanding data retention characteristics and charge loss mechanisms. The following is a summary of charge decay mechanisms in MNOS and SONOS devices proposed in literature [10]:

- 1) Lundkvist, *et al*, [58] have modeled the charge decay behavior of MNOS transistors at room temperature as back tunneling of trapped charge stored in the nitride. The charge in the nitride is assumed to be stored in an area extending from the oxide-nitride interface to about 10 nm into the nitride. This trapped charge tunnels through the tunnel oxide to the silicon substrate due to the internal field present in the retention mode.

- 2) In order to describe the increased rate of loss of charge at elevated temperatures, Lundkvist, *et al.*, [59] proposed that the thermal emission of trapped charges from the nitride is another path of charge decay. It is assumed that the nitride traps are continuously distributed in energy from depth  $\phi_{min}$  to  $\phi_{max}$  in this model.

- 3) Lehovec, *et al.*, [60] assumed that the retention mode loss is limited by the nitride conduction through Poole-Frenkel detrapping. Using this assumption, a simple analytical expression for charge retention in MNOS devices was derived. A mono-energetic trap model was used in their work. Using a numerical data fit for the results, at a trap depth of 1.5 eV, a Poole-Frenkel coefficient of about 6 x

- $10^{-4}$  cm $^{1/2}$ V $^{-1/2}$ eV and an effective escape attempt rate factor of 1.2 x  $10^8$  sec $^{-1}$  were calculated.

- 4) Trap-assisted charge injection was revealed as a major factor in MNOS [61] and SONOS [62] device operations, particularly for thin tunnel oxides at low fields (1-4 MV/cm). Charge tunnels through part of the nitride and the entire thickness of the oxide using a nitride trap as a "stepping stone". It has been revealed that these traps are shallow and are not the same as the traps responsible for charge storage in the nitride, which are much deeper in the nitride.

- 5) White, et al., [18] have explained the charge retention for thin-oxide MNOS memory transistors in terms of the direct tunneling of charges from traps in the nitride to the Si-SiO<sub>2</sub> interface states. A mono-energetic donor and acceptor trap level, localized spatially at the nitride-oxide interface, was considered. They observed a slower rate of charge loss to acceptor Si-SiO<sub>2</sub> interface states as compared with donor Si-SiO<sub>2</sub> interface states. This is interpreted as a result of a larger increase in acceptor interface states near the conduction band edge as compared with donor interface states near the valence band edge.

- 6) Wang and White [63] have expounded on the Yang and White model by examining the contribution of trap-to-band tunneling to the charge decay rate.

### 3.2 Trap Density Modeling

The decay of the charge stored in the nitride layer at room temperature has been

modeled by a number of investigators, such as White and Cricchi [64], Lundkvist, Lundstrom, Svensson [58], Roy and White [65], Kamagaki and Minami [66, 67], and Hu and White [68]. These models invoke back tunneling of charge from the nitride to the semiconductor substrate. An internal field due to trapped charges enhances the process of tunneling.

Figure 3.1: Energy-band diagrams depicting charge loss mechanisms of a conventional SONOS transistor in the write (electrons) and erase (holes) state [69].

The characterization of charge trapped in a nitride dielectric at elevated temperatures has been investigated for SNOS devices [59, 70, 71]. Recently, with the advent of scaled SONOS devices, the temperature dependence has been investigated with an amphoteric trap model [18], which attributes the electron and hole charge storage to a silicon-dangling bond. Their results indicate the trapped 'electrons' in the nitride layer are thermally excited at elevated temperatures and 'back tunnel' through an ultra-thin tunnel oxide to the silicon. In contrast, the distribution of trapped 'holes' is

influenced very little with increasing temperature. This result has been explained [18] by suggesting the electron trap activation energy lies closer to the conduction band edge in the silicon nitride than the activation energy for hole traps to edge of the valence band in the silicon nitride as shown in Fig. 3.1.

Figure 3.2: Amphoteric trap model applied to Si-N bonds in the silicon nitride film. The bond angle  $\theta$  decreases and bond length increases as electrons are trapped due to the attractive and repulsive forces.

Using an amphoteric trap model, an expression has been derived [72] for the charge trapped in the nitride

$$\rho_n(x, E_{TA}, t) = -qg(x, E_{TA})f^{-}$$

(3.1)